# **POWER7<sup>®</sup> System RAS**

## Key Aspects of Power Systems<sup>™</sup> Reliability, Availability, and Serviceability

November 1, 2010

IBM Server and Technology Group Daniel Henderson, Jim Mitchell, and George Ahrens

## Table of Contents

| Introduction                                                                                          | 5  |

|-------------------------------------------------------------------------------------------------------|----|

| The Decade of Smart                                                                                   | 5  |

| Smarter Systems for a Smarter Planet <sup>™</sup>                                                     |    |

| Describing Server Reliability, Availability, Serviceability (RAS)                                     | 6  |

| A Definition of RAS                                                                                   | 7  |

| Reliability                                                                                           |    |

| Availability                                                                                          |    |

| Serviceability                                                                                        | 8  |

| POWER7 Reliability                                                                                    | 9  |

| Overview                                                                                              | 9  |

| Transient Faults                                                                                      | 10 |

| Design and Test                                                                                       | 10 |

| Design Defects                                                                                        | 11 |

| Continuous Reliability Improvement                                                                    | 12 |

| POWER7 Reliability Design Improvements                                                                | 13 |

| Error Detection and Fault Isolation Design                                                            | 14 |

| Introduction                                                                                          |    |

| First Failure Data Capture (FFDC) with Dedicated Service Processors                                   |    |

| Central Electronics Complex Availability                                                              |    |

| Designing for Availability                                                                            |    |

| POWER7 Processor                                                                                      |    |

| A POWER7 Processor Core                                                                               |    |

| Core Recovery – Dynamic Processor Deallocation, Processor Instruction Retry, and Alternate            |    |

| Processor Recovery                                                                                    | 18 |

| Predictive Processor Deallocation                                                                     |    |

| Dynamic Processor Sparing<br>Partition Availability Priority                                          |    |

| Additional POWER7 Processor Core Recovery Design Attributes                                           |    |

| Level 1 Caches (Instruction and Data Cache Handling)                                                  |    |

| Level 2 and Level 3 Caches                                                                            |    |

| Special Uncorrectable Error Handling                                                                  |    |

| CEC nodes and Processor to Processor Interfaces (Fabric Busses)                                       |    |

| Memory Subsystem                                                                                      |    |

| Memory Bus Interfaces                                                                                 |    |

| Memory Buffer                                                                                         |    |

| Memory DIMMs and ECC Words                                                                            |    |

| Scrubbing, Page and Logical Memory Block Deallocation<br>Active Memory Mirroring for Hypervisor       |    |

|                                                                                                       |    |

| Persistent Deallocation of Components and System IPL<br>Detecting and Deallocating Failing Components |    |

| Persistent Deallocation                                                                               |    |

|                                                                                                       |    |

| I/O Subsystem Availability                                                                                       | 32 |

|------------------------------------------------------------------------------------------------------------------|----|

| Base Design                                                                                                      |    |

| Later Developments                                                                                               |    |

| Transitions from PCI to PCI-X and PCI-E and from RIO to RIO-G to InfiniBand                                      |    |

| I/O Hub RAS and I/O Special Uncorrectable Error Handling                                                         |    |

| 12x DDR InfiniBand Connected I/O Hub Adapters and "Freeze" Mode                                                  |    |

| POWER7 I/O Enclosures and Integrated I/O                                                                         |    |

| Attached I/O Availability                                                                                        |    |

| Integrated I/O                                                                                                   |    |

| -                                                                                                                |    |

| Reliability and Availability of the System Infrastructure                                                        |    |

| General System Environments                                                                                      |    |

| Single Server/Operating System Environment                                                                       |    |

| BladeCenter™ and Blades Environment<br>Evaluating the Failure Rate of a "Redundant" and "Passive" Infrastructure |    |

| Standalone Larger SMP Virtualized System Environment                                                             |    |

| Multiple Large Standalone Systems or a Physically Partitioned Single System                                      |    |

| Infrastructure Approach for POWER7 Servers                                                                       |    |

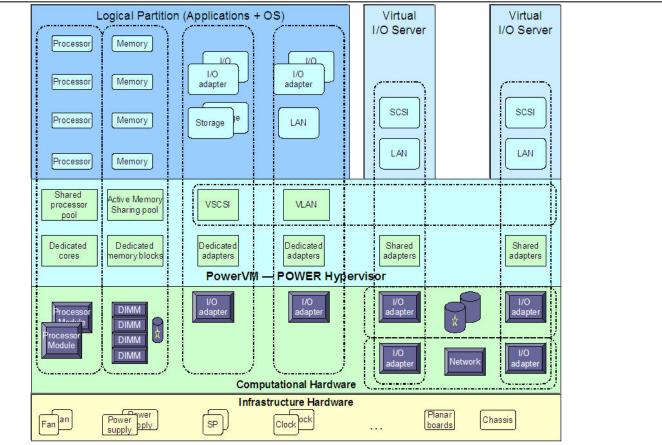

| PowerVM / POWER Hypervisor Design                                                                                |    |

| Processor Resource Virtualization                                                                                |    |

| Memory Resource Virtualization                                                                                   |    |

| Assigning memory to virtual machines                                                                             |    |

| Active Memory Expansion for the Power 795                                                                        |    |

| Mirrored Memory Protects the POWER Hypervisor.                                                                   |    |

| Memory Deconfiguration and Sparing                                                                               |    |

| Dedicated I/O                                                                                                    |    |

| Shared (Virtual) I/O                                                                                             |    |

| Live Partition Mobility                                                                                          | 44 |

| Other Infrastructure Reliability/Availability Design Elements                                                    | 45 |

| Power/Cooling                                                                                                    | 45 |

| TPMD                                                                                                             | 45 |

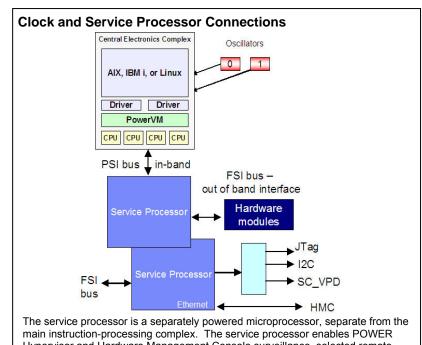

| Clocks                                                                                                           | 45 |

| Service Processors                                                                                               |    |

| Firmware Updates                                                                                                 |    |

| Hardware Management Consoles                                                                                     | 46 |

| Availability and Virtualization beyond the Hardware                                                              | 47 |

| Operating System and Application Features                                                                        | 47 |

| Storage Protection Keys                                                                                          |    |

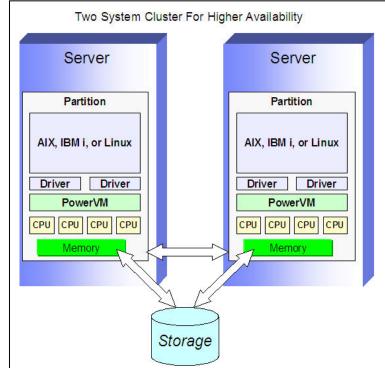

| High Availability Solutions                                                                                      |    |

| A Smarter Planet — Instrumented, Interconnected, and Intelligent                                                 | 49 |

| Appendix A: System Support for Selected RAS Features [ $\bullet$ = available, $\bigcirc$ = optional]             |    |

| Appendix B: Operating System Support for Selected RAS Features [ $\bullet$ = available, $\circ$ = optic          |    |

## Introduction

#### The Decade of Smart

In 2008, the IBM leadership team, recognizing the vast impact of technology on our society, began a dialog on the best ways to create a smarter planet. In a *smarter planet,* intelligence is infused into the systems and processes that make the world work. These technologies encompass both traditional computing infrastructures and the rapidly growing world of intelligent devices: smart phones, global positioning systems (GPS), cars, appliances, roadways, power grids, water systems.

By 2011 we expect almost a trillion devices to be connected to the Internet. These Internet connected devices allow both new modes of social interactions and new ways for businesses to connect to their clients, their employees, and their suppliers. At the same time, these interactions produce enormous amounts of data — raw information about the way people use their resources and how data flows through the marketplace — that can be used to understand how societies operate.

Servers in this environment must have the ability to rapidly process transactions from the Internet, store, and process large amounts of data in backend databases, and support analytical tools allowing business and community leaders to gain the insight needed to make sound, timely decisions within their areas of responsibility.

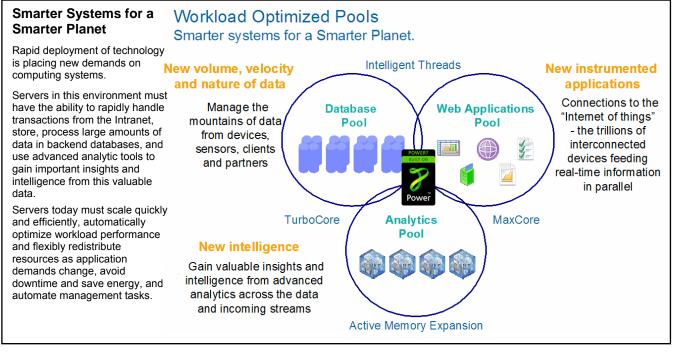

#### Smarter Systems for a Smarter Planet<sup>™</sup>

In February 2010, IBM announced the first models in a new generation of Power Servers based on the POWER7<sup>™</sup> microprocessor. While these new servers are designed to meet traditional computing demands of improved performance and capacity, the transition to "smarter" solutions requires that smarter servers also: scale quickly and efficiently, automatically optimize workload performance and flexibly manage resources as application demands change, avoid downtime and save energy, and automate management tasks.

Therefore, IBM has vastly increased the parallel processing capabilities of POWER7 systems -integrated across hardware and software -- a key requirement for managing millions of concurrent transactions. As expected, the new Power Systems continue to enhance the proud heritage of IBM Power servers — delivering industry-leading transaction processing speed in designs built to efficiently

POW03056.doc

process the largest database workloads. In addition, these new offerings, optimized for running massive Internet workloads, deliver a leap forward in "throughput" computing.

Emerging business models will gather large amounts of data (from the Internet, sensors in electric grids, roads, or the supply chain for example). This data will be deposited in large databases and scrutinized using advanced analytical tools — gleaning information that can provide competitive advantage. Pools of high speed multi-threaded POWER7 processor-based servers can be deployed in optimized pools to efficiently process Internet workloads, store and process large amounts of data in databases, and employ specialized analytic tools (like the IBM Smart Analytics System 7700) to derive information useful to the business. These three computing modes — massive parallel processing, "throughput" computing, and analytics capabilities — are integrated and managed consistently with IBM Systems Director software.

#### Describing Server Reliability, Availability, Serviceability (RAS)

Since the early 1990's, the Power Development team in Austin has aggressively pursued integrating industry-leading mainframe reliability technologies in Power servers. Arguably one of the most important capabilities, introduced first in 1997, is the inclusion of a hardware design methodology called First Failure Data Capture (FFDC) in all IBM Power System servers. This methodology uses hardware-based fault detectors to extensively instrument internal system components. Each detector is a diagnostic probe capable of reporting fault details to a dedicated service processor. FFDC, when coupled with automated firmware analysis, is used to quickly and accurately determine the root cause of a fault the first time it occurs, regardless of phase of system operation and without the need to run "recreate" diagnostics. The overriding imperative is to identify *which component* caused a fault — *on the first occurrence of the fault* — and to prevent any reoccurrence of the error. This feature has been described in detail in a series of RAS technical articles and "white papers" that provide technical detail of the IBM Power design.

The article "Fault-tolerant design of the IBM pSeries<sup>®</sup> 690 system using POWER4<sup>™</sup> processor technology<sup>1</sup>" emphasized how POWER systems were designed — from initial RAS concept to full deployment. In the nine years since the introduction of POWER4, IBM has introduced several successive generations of POWER processors, each containing new RAS features. Subsequent white papers<sup>2,3</sup> included descriptions of how RAS attributes were defined and measured to ensure that RAS goals were in fact being met and detailing how each new feature contributed to reliable system operations. In general, these documents outlined the core principles guiding IBM engineering design that are reflected in the RAS architecture. A user should expect a server to provide physical safety, system integrity, and automated fault detection and identification.

- 1. Systems should be reliable in a broad sense: they should

- produce accurate computational results

- be free of physical hazards

- be free of design flaws that impact availability or performance

- have few hardware failures over their serviceable life

- 2. Systems should be configurable to achieve required levels of availability

- Without compromising performance, utilization or virtualization

- Utilizing Industry leading availability design and practices

- Capable of taking advantage of clustering techniques to achieve the highest levels of availability

- 3. Systems should diagnose problems automatically and proactively

<sup>&</sup>lt;sup>1</sup> D.C.Bossen A. Kitamorn, K.F. Reick, and M.S. Floyd, "Fault-tolerant design of the IBM pSeries 690 system using POWER4 processor technology", IBM Journal of Research and Development, VOL.46 NO.1, January 2002.

<sup>&</sup>lt;sup>2</sup> J. Mitchell, D. Henderson, G. Ahrens, "IBM @server p5: A Highly Available Design for Business-Critical Applications", p5tiPOWER5RASwp121504.doc, December 2004.

<sup>&</sup>lt;sup>3</sup> J. Mitchell, D. Henderson, G. Ahrens, and J. Villarreal, "Highly Available IBM Power Systems Servers for Business-Critical Applications", PSW03003-USEN-00, April 2008.

- Taking advantage of self-healing and selective deconfiguration where possible to keep applications running

- · Without relying on diagnostics to recreate problems, or manual analysis of dumps

- Without relying on assistance from the operating system or applications

The intent of this white paper, then, is to highlight POWER7 server design features that extend the inherent Power Architecture<sup>®</sup> RAS capabilities delivered in previous server generations.

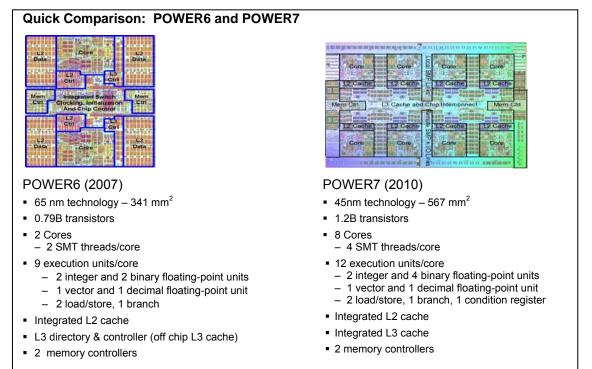

The POWER7 module is a much denser chip than its POWER6<sup>®</sup> predecessor, containing eight cores instead of two, and featuring 32 MB of integrated, not external, L3 cache. Compared to POWER6 it also includes substantially more function, with higher levels of simultaneous multi-threading (SMT) per core.

In addition to advances in density, virtualization, and performance the processor module also contains substantial new features related to reliability and availability, building on the rich heritage of prior generations.

Emphatically, a system's reliability, and the availability of the applications it supports, is a function of much more than just the reliability of the processors, or even of the entire system hardware. A full description of a system design for RAS must include all of the hardware, the firmware, the operating system, middleware, applications, operating environment, duty cycle, and so forth.

## A Definition of RAS

As there are many ways to define reliability, availability, and serviceability, perhaps a good way to begin this discussion is to describe the how the IBM engineering team views RAS. A somewhat technically imprecise but useful definition for server hardware:

#### Reliability

• How infrequently a defect or fault is seen in a server.

#### Availability

How infrequently the functionality of a system or application is impacted by a fault or defect.

#### Serviceability

How well faults and their impacts are communicated to end-users and servicers and how efficiently and non-disruptively they are repaired.

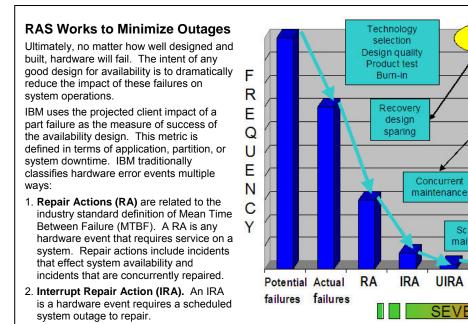

Defined this way, reliability in hardware is all about how often a hardware fault requires a system to be serviced – the less frequent the failures, the greater the reliability. Availability, then, is how infrequently such a failure impacts the operation of the system or application. For high levels of availability, correct system operation must not be adversely affected by hardware faults. In other words, a highly available system design insures that most hardware failures will not result in an application outage. Serviceability concerns itself with identifying what fails and ensuring an efficient repair (of that component, firmware, or software).

- 3. Unscheduled Incident Repair Action (UIRA). A UIRA is a hardware event that causes a system to be rebooted in full or degraded mode. The system will experience an unscheduled outage. The restart may include some level of capability loss, but remaining resources are made available for productive work.

- 4. High Impact Outage (HIO). A HIO is a hardware failure that triggers a system crash that is not recoverable by immediate reboot. This is usually caused by failure of a component that is critical to system operation and is, in some sense, a measure of system single points-of-failure. HIOs result in the most significant availability impact on the system, since repairs cannot be effected without a service call.

The clear design goal for Power Systems is to prevent hardware faults from causing an outage: platform or partition. Part selection for reliability, redundancy, recovery and self-healing techniques, and degraded operational modes are used in a coherent, methodical strategy to avoid application outages.

Minimize num ber

of repair actions

Minimize impact

of repair action

Minimize repair

action

duration

Unscheduled

maintenance

Scheduled

maintenance

HIO

UIRA

SEVERIT

## **POWER7** Reliability

### Overview

A variety of metrics can be used to describe the reliability or availability of a system or component. One of the most common is Mean Time between Failure (MTBF) which is traditionally thought of as how long, on average, something can be used before it stops working correctly.

When component description states that it has a MTBF of 50 years, the intent is not to claim it would be expected to run 50 years before seeing a failure. Rather, this statistical measurement indicates that in a large population of components, while the likelihood of any individual part failure is small, one could expect that 2% of the components would fail each year (for example, on a server with a published 50 year MTBF, if 100 servers were in operation for a year, an average of two server failures would be experienced).

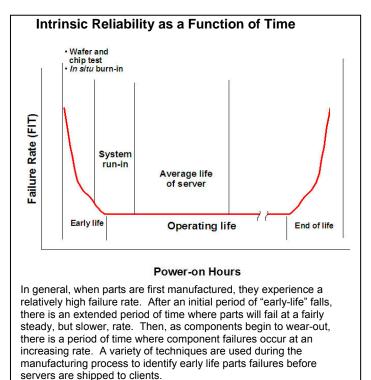

This can be understood best by looking at the way hardware in a system is intrinsically expected to fail. Experience indicates that newly manufactured parts experience a relatively high failure rate. After an initial period of "early-life" fallout, there is an extended period of time where parts will fail at a fairly steady, but slow, rate. Then as components begin to wear-out there is a period of time where failures occur at an increasing rate.

This can be illustrated by charting failures over time. A graph of typical failure rates is informally called a "bath-tub" curve — reflecting its unique shape.

It is the intent of the RAS design for POWER servers that systems be tested, screened, and if necessary "burned-in" such that when systems are delivered to clients for installation, components that can cause an outage are already "past" the early-life failure portion of the bath-tub curve.

In addition, the RAS design is intended to ensure that the wear-out portion for outage producing parts would be encountered after systems have been retired from production.

A number of different elements come in to play to make the latter expectation a reality. To mention a few:

- Components with a significant expectation of wearing out: fans, power components, etc. are made redundant and concurrently repairable or otherwise accounted for in the design such that their failures do not lead to planned or unplanned outages.

- The thermal environments of systems are regulated and monitored to ensure that components do not wear out quickly due to thermal stress.

• Spare connector pins are added to connectors that might show a propensity to fail after extended use (due to corrosion and other factors).

POW03056.doc

## **Transient Faults**

Component failures ("hard" failures related to their intrinsic reliability) are not the only source of hardware outages. A variety of temporary or transient error may occur when the underlying hardware is not defective. These include faults caused by transient external upsets such as power line disturbances, static electrical discharge, energy released into circuits by cosmic radiation, and occasional circuit disturbance due to other sources of random noise.

Designing reliable systems require that the sources of these potential transient upsets be understood —so that hardware can be appropriately protected from them.

To this end, engineers use components and design techniques that inherently protect components and subsystems against transient errors: for example, using a processor latch design that is generally tolerant of the energy released by a cosmic ray strike.

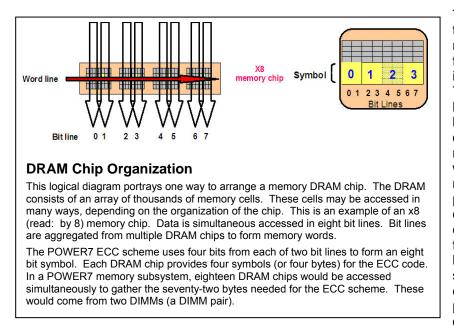

Techniques are also employed to allow recover from problems as they occur. For example, by using a double error detect/single error correction (DEC/SEC ECC) code in memory; a temporary upset in a single bit can be automatically corrected.

#### Design and Test

Resilient system design techniques, component selection for reliability, thermal management, and controlling voltage regulation are some of the techniques used by the IBM system engineering team to meet the challenge of transient faults.

#### A Test to Verify Automatic Error Recovery<sup>4</sup>

To validate the effectiveness of the RAS techniques in the POWER6 processor, an IBM engineering team created a test scenario to "inject" random errors in the cores.

Using a proton beam generator, engineers irradiated a POWER6 chip with a proton beam, injecting high-energy protons into the chip at many orders of magnitude higher flux than would normally be seen by a system in a typical application. The team employed a methodical procedure to correlate an error coverage model with measured system response under test.

The test team concluded that the POWER6 microprocessor demonstrated dramatic improvements in soft-error recovery over previously published results.

#### Extending the testing to POWER7

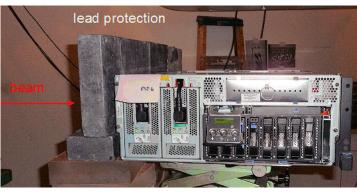

This year, an IBM engineering team conducted a series of proton beam and "hot underfill" tests on the POWER7 microprocessor to validate the system design and the inherent recovery procedures.

POWER7 test system mounted in beam line.

POWER7 includes extensive soft error recovery techniques including Instruction Retry and Alternate Processor Recovery, providing "immunity" from errors that could cause outages on other processor designs.

In one test, engineers underfilled six POWER7 modules with radioactive material and ran them in Power 780 systems, amassing thousands of hours of highly accelerated runtime. This method speeds testing by dramatically increasing the likelihood of experiencing soft errors in the POWER7 chip. This test — equivalent to running for approximately a million years in a normal operating environment — generated almost 26,600 induced transient errors. Only 3 resulted in a UIRA — this is an equivalent soft error MTBF UIRA of greater than 330,000 years.

This type of system checking allow the engineering team to extensively identify issues with the recovery strategy and implementation, and validate checker coverage, checker priorities, and the latch and array designs.

#### Proton beam injection

- Irradiated a POWER7 module with proton beam

Injecting 720 billion high-energy protons

- Many orders of magnitude higher flux than normal

- Validating detection/resilience and recovery mechanisms in the module

#### Hot under-fill testing

- Replaces a radiation-free under-fill material (Intended to shield against alpha-particles) with an irradiated under-fill intended to expose modules to alpha-particle energy

- Tests operating modules in systems over an extended time period

- Validating the server's soft errors correction facilities

<sup>&</sup>lt;sup>4</sup> Jeffrey W. Kellington, Ryan McBeth, Pia Sanda, and Ronald N. Kalla, "IBM POWER6 Processor Soft Error Tolerance Analysis Using Proton Irradiation", SELSE III (2007).

However, simply designing for reliability is not sufficient to ensure robust protection against transient faults. IBM has long recognized the need to test systems to validate their resistance to sources of soft error events. Compliance testing of systems at IBM includes subjecting systems to power line disturbances of various different intensities and durations, including those that might be created by nearby lightening strikes, systematically exposing systems to electrical static discharge, doing thermal testing and profiling, and so forth.

In more recent years IBM has also expended considerable effort in exposing electronics to large doses of radiation (many orders of magnitude more intense than seen in the field) to ensure that the designs provide the intended level of protection from cosmic and alpha particle emissions.

## **Design Defects**

Sometimes, a system design flaw (a "bug" in the hardware or firmware) is manifested as an unplanned outage. This is most typically the case for those infrequent design defects that occur only under a very specific set of operating conditions. These rarely seen situations can be very difficult to identify and repair. In other cases, defects in the methods used to handle error detection or recovery can themselves be defective, resulting in cascading errors and leading to system outages.

Predicting system outages (determining the system reliability) caused by intrinsic failures is complex but relatively straightforward. Reliability calculations can also account for the predicted impact of transient errors. It is very difficult, however, to include the impact of to design defects in these computations.

Rather than projecting the impact of design defects, a good reliability design strives to eliminate them. For this reason processors and other custom modules designed by IBM are extensively simulated before parts are fabricated. Simulation is intended to validate both the function of the devices, and the system's ability to detect and handle errors as they occur. Component level simulation and testing is the starting point in a multi-tiered system verification strategy performed before a product is released. Engineers create full system computational environments in which entire stacks — hardware, firmware, operating system, and applications — are functionally tested in the ways users are expected to deploy systems.

IBM has invested heavily in a hardware design that supports error detection and correction during normal operations. This approach also incorporates the ability to inject errors as needed during the design bring-up and validation phase to efficiently and thoroughly confirm a system's functions and its' error handling capabilities.

Power Systems use a FFDC methodology, employing an extensive array of error checkers and Fault Isolation Registers (FIR) to detect, isolate, and identify faulty conditions in a server. This type of automated error capture and identification is especially useful in allowing quick recovery from unscheduled hardware outages. While this data provides a basis for component failure analysis, it can also be used to both improve the reliability of the part and as a starting point for design improvements in future systems.

IBM RAS engineers use specially designed logic circuitry to create faults that can be detected and stored in FIR bits, simulating internal chip failures. This technique, called error injection, is used to validate server RAS features and diagnostic functions in a variety of operating conditions (power-on, boot, and operational run-time phases). Error injection is used to confirm both execution of appropriate analysis routines and correct operating system, and Service Focal Point and Service Agent applications). Further, this test method verifies that recovery algorithms are activated and system recovery actions take place. Error reporting paths for client notification, pager calls, and call home to IBM for service are validated and RAS engineers substantiate that correct error and extended error information is recorded. A test servicer, using the maintenance package, then "walks through" repair scenarios associated with system errors, helping to ensure that all the pieces of the maintenance package work together and that the system can be restored to full functional capacity. In this manner, RAS features and functions, including the maintenance package, are verified for operation to design specifications.

#### Continuous Reliability Improvement

Of course, setting failure rate reliability targets for components, designing systems to meet specific availability metrics, thoroughly validating and testing the reliability design, and projecting the expected resulting performance all help create a reliable server design. However, simply setting targets and simulating the design is not sufficient.

It is also vital for long term system reliability that the performance of deployed systems be monitored, deficiencies identified, and corrective actions taken to ensure continued reliability of systems over time.

IBM field engineering teams track and record repairs of system components covered under warranty or maintenance agreement. Failure rate information is gathered and analyzed for each part by IBM commodity managers, who track replacement rates. Should a component not be achieving its reliability targets, the commodity manager will create an action plan and take appropriate corrective measures to remedy the situation.

Aided by IBM's FFDC methodology and the associated error reporting strategy, commodity managers build an accurate profile of the types of field failures that occur and initiate programs to enable corrective actions. In many cases, these corrections can be initiated without waiting for parts to be returned for failure analysis.

The IBM field support team continually analyzes critical system faults, testing to determine if system firmware, maintenance procedures, and tools are effectively handling and recording faults. This continuous field monitoring and improvement structure allows IBM engineers to ascertain with some degree of certainty how systems are performing in client environments rather than just depending upon projections. If needed, IBM engineers use this information to undertake "in-flight" corrections, improving current products being deployed. This valuable field data is also used to plan and design future servers.

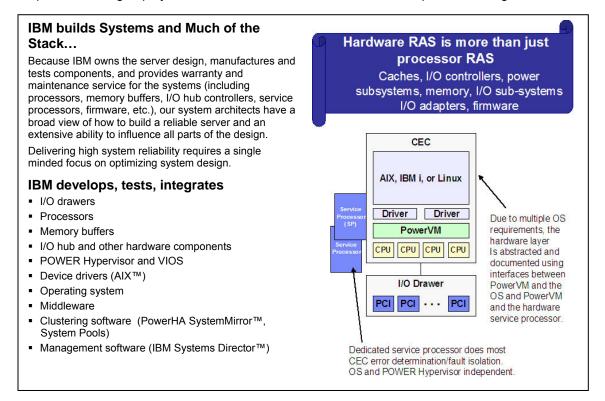

Because IBM owns the server design, manufactures and tests components, and provides warranty and maintenance service for the systems (including processors, memory buffers, I/O hub controllers, service processors, firmware, etc.), IBM system architects have a broad view of how to build a reliable server

POW03056.doc

and an extensive ability to influence all parts of the system design. When designing a specific component there is a natural tendency to want to build the "best" or the "fastest." The risk is that while a component may be optimized by some criteria, it may not operate well within a system's architecture. This type of design process is referred to as sub-optimization — components work well by themselves but the overall server performance or reliability suffers. This type of server design can result when a vendor receives components from a variety of sources and tries to "glue" systems together.

A primary objective of the IBM Power design team is to deliver "smarter" systems that provide balanced performance (coupling processor speed, with memory capacity and I/O bandwidth) and that integrate exceptionally well with systems software (operating system, middleware, applications).

IBM is uniquely positioned in the computing industry in that IBM designs and builds, (or IBM engineers specify the design and monitor and verify the manufacture), integrates, and tests system key components — transforming raw silicon to servers, integrating OS, middleware, and management software. This control extends to IBM engineers a very efficient means to optimize solutions — whether a change is needed in the hardware or firmware design, or in how it is manufactured, tested, or serviced.

## POWER7 Reliability Design Improvements

From a RAS standpoint, the system design process begins with the definition of a design for reliability. An IBM corporate directive dictates that new products must deliver equal or better reliability than their predecessors. This outcome is expected even though each new server generation typically delivers improved performance and higher capacity — often at the "cost" of more components that can fail (more cores, memory, I/O channels).

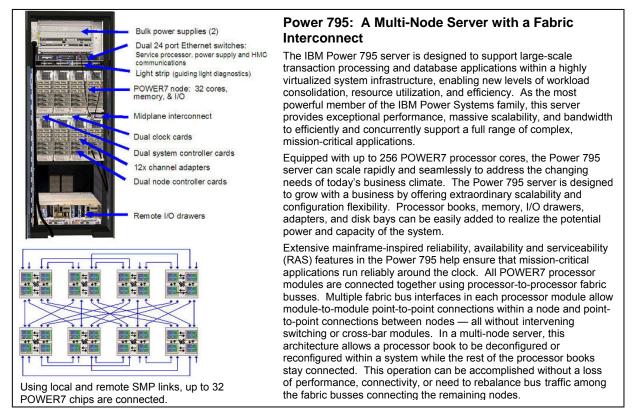

The transition from POWER6 to POWER7 presented an interesting challenge for the RAS team. On one hand, the dramatic increase in number of cores per chip allows IBM to deliver servers with the same number of cores but with many fewer processor chips (fewer potential points of failure). In addition, the POWER7 incorporates an integrated L3 cache — reducing the number of chips required in larger server designs. On the other hand, IBM is also delivering servers with many more cores (up to 256 in the Power 795) — along with dramatic increases in the memory and I/O required to keep those cores working at optimal levels of performance.

As an additional challenge to RAS engineers, stepping down the processor feature size to 45nm technology brought a potential increase in exposure to transient errors. IBM introduced both Instruction Retry and Alternate Processor Recovery in POWER6 processor-based servers to help avoid these types of soft errors. POWER7 continues this technology and extends its overall resistance to these types of events by using a "stacked latch" design which is inherently less likely to change state when an energy discharge from a cosmic ray or alpha particle is encountered.

Continuing to focus on avoiding soft errors, the memory bus on POWER7 processor-based servers features a differential design with the ability to tolerate soft errors by detecting faults with CRC checking and retrying faulty operations. The bus maintains the ability introduced in POWER6 to replace a faulty data bit line on the bus with a spare bit line dynamically.

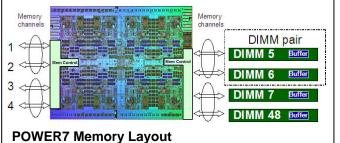

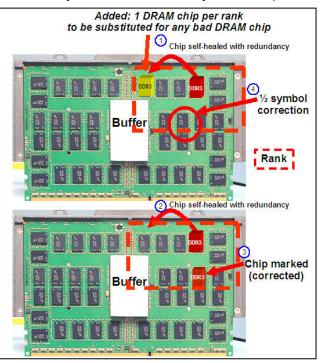

Significantly, given the expectations for dramatically increasing the overall amount of memory available in the system, the amount of spare memory capacity on custom DIMMs for larger servers has also increased in POWER7. Using spare DRAM chips, selected high end POWER7 servers provide a "self-healing capability" in memory, automatically moving data from failed DRAM chips to available spares. This design permits a pair of DIMMS, on a rank basis, to experience one and sometimes two DRAM failures without replacing the DIMMs and still maintain Chipkill detection and correction capabilities (potentially surviving three DRAM chip failures for every rank pair on a DIMM pair). For details, refer to Memory DIMMS and ECC Words on page 27.

## **Error Detection and Fault Isolation Design**

## Introduction

In a broad sense, for systems to be reliable, faults which could impact computations must be detected and corrected so that incorrect results are not propagated to client applications. Systems designed to accomplish this task require an extensive architecture for error detection, recovery, and fault isolation.

Such an infrastructure must include the ability to detect and, where possible, correct errors in data wherever it is stored. Maintaining at least double bit detection and single bit correction ECC codes to verify stored data can help meet that objective.

However, while the sheer number of circuits devoted to such ECC correction codes can be large, error detection should include much more than just ECC data checking. To be effective, it should also include:

- The ability to detect cases where data is stored in, or retrieved from, an incorrect location, or where there was no response to a request to store or retrieve data.

- Mechanisms to validate that the logic function of various processing components and those devoted to data movement were also free of flaws. For example:

- Error detection and correction of data in latches and arrays used to store logic state.

- Processes that flag invalid state machine transitions caused by component failures and transient conditions

- Mathematical mechanisms for statistically validating the results produced by computation units (e.g., using techniques like residue checking).

To ensure efficient servicing of systems having uncorrectable errors, a complete design methodology must not only detect an error, it must also include enough data to determine the source of the error — to correctly identify a specific component (or components). These parts may need to be deconfigured to prevent a re-occurrence of a problem, and ultimately replaced as required.

This architecture mandates that error checkers be distributed throughout the system to allow identification of the root cause of a failure. For instance, it is not sufficient to simply check the validity of data (via a mechanism such as ECC) when it is loaded into a processor data cache or written to memory. The data must be validated at every point where it crosses a component boundary (everywhere it could be corrupted).

For the highest levels of error detection and recovery, a server must both identify a fault when it occurs *and* incorporate a mechanism to automatically handle the failure *at that time*.

For example, such a design might mandate that a floating point execution unit complete the residue checking of an executing floating point instruction before the next instruction begins, so that a failed instruction can be retried immediately should an error occurs.

Finally, error detection and fault isolation should be:

- Accomplished automatically in the hardware and firmware without the need for errors to be recreated by a diagnostic program and without the need for any sort of human interpretation of error indicators.

- Completed in hardware/firmware *independent of any operating system*, and ideally also independent of system processing resources (so that the server hardware can efficiently support multiple operating systems and avoid reducing the computational resources available to the system).

## First Failure Data Capture (FFDC) with Dedicated Service Processors

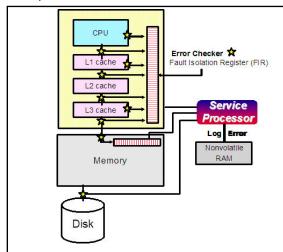

Components in the central electronics complex (processors, memory buffers, and I/O hub controllers) use hardware-based fault detectors to extensively instrument internal system components.

Called First Failure Data Capture, this architecture requires that a server "build-in" hardware error check stations that capture and help to identify error conditions. A 256-core Power 795 server, for example, includes over 598,000 checkers to help capture and identify error conditions. These are stored in over 96,000 Fault Isolation Register bits. Each detector is a diagnostic probe capable of reporting fault details to a dedicated service processor. Pertinent error data related to the fault is captured and collected in fault isolation registers and processed with specialized "who's on first" logic for analysis.

With this technique, if a fault is detected in a server, the root cause of the fault will typically be captured without the need to recreate the problem or run any sort of extended tracing or diagnostics program. For the vast majority of faults, a good FFDC design means that the root cause can also be detected automatically without servicer intervention.

The service processor is a dedicated microprocessor, independent of the POWER7 microprocessors, used to correlate fault information and to orchestrate error recovery mechanisms in conjunction with the hardware and POWER Hypervisor (firmware). The service processor is signaled whenever the status of the fault isolation registers change and can access the register information at any time without impacting the performance of these modules.

First Failure Data Capture plays a critical role in delivering servers that can self-diagnose and self-heal. Using thousands of checkers (diagnostic probes) deployed at critical junctures throughout the server, the system effectively "traps" hardware errors at system run time.

The separately powered service processor is then used to analyze the checkers and perform problem determination. Using this method, IBM avoids the commonly used intermittent "reboot and retry" error detection strategy, since the system knows with some certainty which part is having problems. In this automated approach, run-time error diagnostics can be deterministic, so that for every check station, the unique error domain for that checker is defined and documented. Ultimately, the error domain becomes the FRU (part) call, and manual interpretation of the data is not normally required. I/O adapters and devices physically assigned to partitions typically manage error detection and reporting partitions Operating System device drivers.

This architecture is also the basis for IBM's predictive failure analysis, since the service processor can now count, and log, intermittent component errors and can deallocate or take other corrective actions when an error threshold is reached.

#### **Central Electronics Complex (CEC)**

- Built-in hardware error checkers

- Detect faults where and when they occur

- Isolate faults to the failing component or interface

✓ Handle error reporting so that the original error source is identified before side-effects are propagated

- Record information in special Fault Isolation Registers

- Hardware/firmware takes appropriate internal actions to

Automatically recover from faults where possible

- Notify service processor or Hypervisor of recoverable errors

- Take necessary actions to minimize damage associated with unrecoverable errors

- No need to recreate problems for fault identification/isolation

#### Service Processor

- Receives error reports and reads Fault Isolation Registers

- Takes action on faults:

- Implements recovery actions

- Enables self-healing features

- Deallocates resources

- ✓ Predictively based on frequency of events (thresholds)

- $\checkmark$  In response to error reports

- Handles unrecoverable errors

- Collects additional extended failure information

- Initiates partition or system recover actions as configured

- The POWER Hypervisor may handles some types of errors

#### **Operating systems and applications**

- Not involved in error detection/fault isolation or recovery of CEC component failures

- Error detection and fault isolation of these are highly independent of the Operating Systems (no requirement to change OS to take advantage of most RAS features).

- May assist in dynamic processor deallocation in some circumstances

- Predictively deallocate dedicated cores or memory pages

- Terminate applications for uncorrectable memory errors

The RAS architecture, then, couples FFDC with *automated* firmware analysis, to quickly and accurately determine the root cause of a fault the first time it occurs, regardless of phase of system operation and without the need to run "recreate" diagnostics. The overriding imperative is to identify *which component* caused a fault — *on the first occurrence of the fault* — and to prevent any reoccurrence of the error.

IBM engineers control the entire CEC design (from silicon to architecture) and the RAS architects correlate error events over the entire system. To help insure accurate error coverage and identification, Power Servers include an *additional* error infrastructure to help identify the first cause of a fault even if it propagates to multiple components (e.g. data from memory having uncorrectable errors).

In addition to accessing fault isolation registers, when a severe error occurs, the service processor also has the ability to scan the state of functional latches in modules, to create a snapshot of the state of the processors and other components at the time of a failure. This additional information, referred to as extended error data, can be transmitted to IBM when a failure occurs, using automated call-home functions (when enabled by the system administrator), so that IBM servicers can ascertain the circumstances surrounding a fault event. This process enables detailed failure analysis, helping to ensure that systematic issues can be quickly identified and dealt with as part of a continuous quality improvement process [See <u>Continuous Reliability Improvement</u> on page **Error! Bookmark not defined.**].

## **Central Electronics Complex Availability**

#### Designing for Availability

The IBM Power availability strategy is deeply rooted in an extensive history spanning decades of mainframe development. By leveraging an extensive background in Predictive Failure Analysis<sup>™</sup> and dynamic system adaptation, the IBM availability team has helped to create a unique processor that unleashes significant value to the client.

Together these attributes form a cornerstone of the POWER7 availability strategy as delivered in the, Power Server family. These capabilities enable an unprecedented level of self-awareness in POWER7 processor-based systems. The FFDC method allows the system to proactively analyze situations that indicate an impending failure, in many cases removing the questionable component from use before it can cause a threat to system stability.

To qualitatively understand the availability design of Power Systems it's necessary to identify the availability characteristics of each component of the system. This is true of hardware – processors, memory, I/O adapters, power and cooling subsystems, chassis and firmware as it relates to the function of the hardware — and of each software component used on the server. Thus, even if a RAS discussion is limited to hardware elements, it must be investigated in the context of the entire system — and not just focus on one element, such as a processor core, or memory component.

In the sections that follow, the discussion of RAS capabilities will specifically spotlight the capabilities delivered in the high-end enterprise class systems. Server design methodologies commonly focus first on the very stringent availability requirements of large, highly virtualized, high performance systems like the Power 795. RAS features developed for this class of systems will then frequently "flow down" through the product line, exploiting investments in processor or firmware recovery design, and delivering "high end" availability attributes to "entry" class servers. A RAS feature matrix by model is provided in <u>Appendix A</u>: <u>System Support for Selected RAS</u> Features [page 51].

## POWER7 Processor

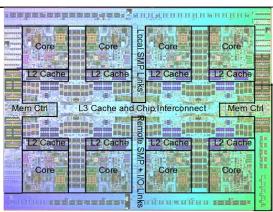

#### POWER7 Processor Chip

The POWER7 chip features eight cores each capable of single- and simultaneous multithreading execution (including the ability to execute four threads on the same core at the same time). POWER7 maintains binary compatibility with existing POWER6 processor-based systems to ensure that binaries continue executing properly on the newer systems. Supporting virtualization technologies like its POWER6 predecessor, the POWER7 technology has improved availability and serviceability at both chip and system levels. To support the data bandwidth needs of an eight-core processor running

at 4 GHz (or in TurboCore mode at 4.25 GHz), the POWER7 chip uses embedded dynamic RAM (eDRAM) technology to include a 32-MB intelligent L3 cache on the processor chip. This cache dramatically reduces the latency of data access when compared to an external cache implementation, while taking roughly 1/3 the space and 1/5 the standby power while delivering significant improvements in resistance to soft errors when compared to conventional static RAM (SRAM).

Based on a superscalar design, each 4W SMT core in the POWER7 microprocessor includes twelve (12) instruction execution units. Delivering recovery hardware for processor Instruction Retry for automatic restart of workloads on the same, or alternate, core in the same server, the POWER7 chip also uses a "stacked latch" design for improved soft error immunity and includes a wide variety of features for energy management including "sleep" and "nap" modes and dynamic frequency and voltage management.

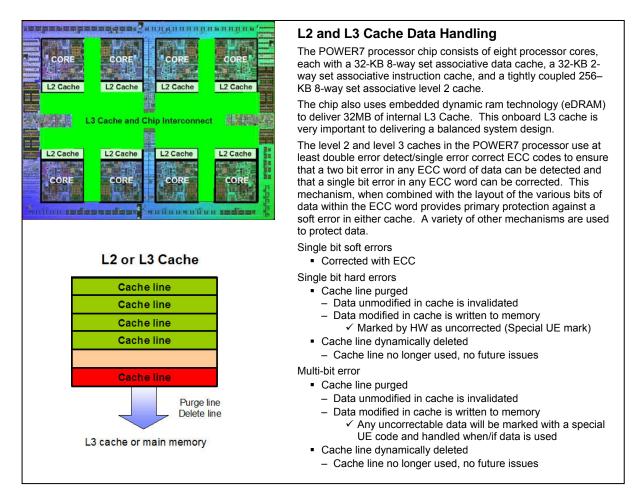

The POWER7 processor chip consists of eight processor cores, each with a 32-KB 8-way set associative data cache, a 32-KB 2way set associative instruction cache, and a tightly coupled 256–KB 8way set associative level 2 cache.

The chip also uses embedded dynamic RAM technology (eDRAM) to deliver 32MB of *internal* L3 Cache. This onboard L3 cache is very important to delivering a balanced system design as it

#### provides:

- Up to a 6 to 1 latency improvement for L3 accesses vs. external L3 since there are no off-chip drivers or receivers in the L3 access path.

- A 2 times bandwidth improvement with on-chip interconnect.

- A space reduction over conventional SRAM.

- $\checkmark$  1/3 the space of conventional SRAM implementation.

- $\checkmark$  1/5 the standby power.

- An innovative, intelligent cache design, with a 4-MB fast L3 region per processor core where the system:

- ✓ Will automatically migrate private footprints (up to 4-MB) to this fast local region (per core) at ~5X lower latency than full L3 cache.

- ✓ Can automatically clone shared data to multiple private regions.

POWER7 also includes two memory controllers (each with 4 high speed memory channels), and a series of bus controllers that manage interfaces to other processor modules, to I/O hub controllers, and to a service processor.

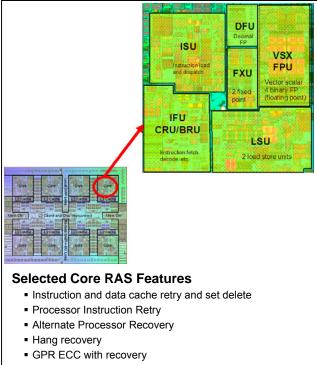

## A POWER7 Processor Core

Each 64-bit processor core features "out-of-order" instruction execution, and includes the ability to dispatch 6 instructions per cycle and issue 8 instructions per cycle. Each core supports 12 instruction execution units, including 2 for fixed point (integer) processing (FXU), 2 load/store (LSU), 4 double precision floating point processors (FPU), 1 vector processor (VMX), 1 branch (BRU), 1 condition register (CRU), and 1 decimal floating point unit (DFU).

Core contained checkstop

#### A POWER7 Processor Core

Each 64-bit processor core features "out-of-order" instruction execution, and includes the ability to dispatch 6 instructions per cycle and issue 8 instructions per cycle. Each core supports 12 instruction execution units, including 2 for fixed point (integer) processing, 2 load/store, 4 double precision floating point processors, 1 vector processor, 1 branch, 1 condition register, and 1 decimal floating point unit.

Each variable frequency core (up to 4.25 GHz) can process instruction streams in single threaded, or 2- or 4-way simultaneous multi-threaded (SMT) mode. SMT modes may be dynamically set per virtual machine or changed by the operating system at run-time for optimal performance.

To achieve the highest levels of server availability and integrity, FFDC and recovery safeguards must protect the validity of user data anywhere in the server, including all the internal storage areas and the buses used to transport data. It is equally important to authenticate the correct operation of internal latches (registers), arrays, and logic within a processor core that comprise the system execution elements and to take appropriate action when a fault ("error") is discovered.

The POWER7 microprocessor includes circuitry (FFDC) inside the processor core to spot and correct these types of errors. A wide variety of techniques is employed, including built-in precise error check logic to identify faults within controller logic and detect undesirable conditions within the server. In addition, Power Servers can use Predictive Failure Analysis techniques to vary off (dynamically deallocate) selected components before a fault occurs that could cause an outage (application, partition, or server).

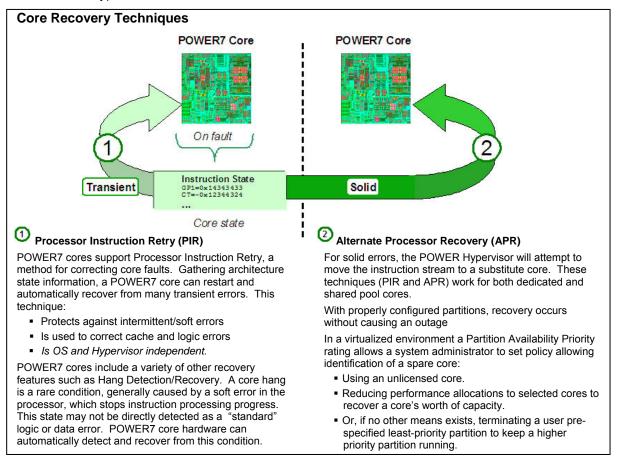

## Core Recovery – Dynamic Processor Deallocation, Processor Instruction Retry, and Alternate Processor Recovery

The POWER6 processor-based servers introduced a core design that included extensive facilities to detect and isolate a wide variety of errors during instruction processing. Maintaining an accurate copy of CPU state, the core could retry a failing instruction, avoiding many soft failures.

These systems introduced a number of features enabling dynamic adjustments when issues arise to threaten availability. Most notably, they implement the Processor Instruction Retry suite of tools, which includes Processor Instruction Retry, Alternate Processor Recovery, Partition Availability Prioritization, and Single Processor Checkstop. Taken together, in many failure scenarios these features allow a Power Server (POWER6 or POWER7) to recover transparently without an impact on a partition using the core. This feature set is described in detail in a POWER6 RAS white paper.<sup>5</sup>

*Processor Instruction Retry* (retrying a failed operation caused by a transient error), is a primary means by which a POWER6 or POWER7 system recovers from "soft" faults in the processor core. These processor chips also include soft error fault handling mechanisms that operate in cooperation with the POWER Hypervisor. These transient error recovery techniques are accomplished without operating system involvement.

However, while protecting against transient or soft errors is an important availability concern, it is not sufficient for a complete RAS design. Engineers must also take into account the "solid" failure rate of components. For this reason, POWER6 incorporated a mechanism that created a checkpoint describing the core operational state before an instruction was executed. Then, in many cases, the POWER Hypervisor could load the state information from a solidly failing processor core into an alternate

<sup>&</sup>lt;sup>5</sup> Jim Mitchell, Daniel Henderson, George Ahrens, and Julissa Villarreal, "IBM Power Platform Reliability, Availability, and Serviceability (RAS). Highly Available IBM Power Systems Servers for Business-Critical Applications", POW03003-USEN-03 (June 5 2009).

processor core — dynamically moving thread execution without an application outage. This technique is called *Alternate Processor Recovery*. Alternate processor recovery allowed systems to recover from a number of solid faults in the processor that would otherwise have caused outages of either partitions or entire systems. This feature is now supported in POWER7 servers.

A key aspect of this design is that all of this capability for recovery, for both hard and soft failures, is contained in the hardware and POWER Hypervisor. Recovery is expected to be transparent to applications and independent of the operating systems deployed in partitions.

If a processor-detected fault cannot be recovered by Processor Instruction Retry or Alternate Processor Recovery, then the POWER Hypervisor will terminate (checkstop) the partition using the processor core at the time of the fault. This is known as *core contained checkstop*. In general, this limits the outage to the single partition. However, if a fault can not be contained to a single instruction, or if a failure occurred on a POWER Hypervisor instruction, the server will be rebooted.

#### Predictive Processor Deallocation

Prior to the introduction of the advanced core recovery features in POWER6, Predictive Processor Deallocation was the primary means for dealing with core errors. This feature considers patterns of correctable errors in processor function as predictive of a future uncorrectable processor error.

Dynamic Processor Deallocation enables automatic deconfiguration of an error-prone processor core before it causes an unrecoverable system error (unscheduled server outage). Dynamic Processor Deallocation relies upon the service processor's ability to use FFDC-generated recoverable error information and to notify the POWER Hypervisor when the processor core reaches its predefined error limit. The POWER Hypervisor, in conjunction with the operating system (OS), will then "drain" the runqueue for the offending core, redistribute the work to the remaining CPUs, deallocate the offending CPU, and continue normal operation, although potentially at a lower level of system performance

This feature could be coupled with Dynamic Processor Sparing to automatically and dynamically substitute available spare processing capacity prior to deallocation of the failing core.

While this technique is still used in POWER7 servers, it has some significant drawbacks when compared to Processor Instruction Retry and Alternate Processor Recovery:

- When processors are dedicated to partitions, cooperation in the deallocation by the operating system and or applications is required to ensure that the thread currently running on the processor is completed before the deallocation takes place.

- This mechanism recovers from predictable, recoverable errors. Unpredictable intermittent or solid errors can not be handled.

#### **Dynamic Processor Sparing**

IBM's Power virtualization environment built on PowerVM<sup>™</sup> offers a secure virtualization environment that can help eliminate underutilized servers by pooling resources and optimizing their use across multiple application environments and operating systems. Through advanced dynamic logical partitioning (LPAR) capabilities, a single partition can act as a completely separate AIX<sup>®</sup>, i, or Linux<sup>™</sup> operating environment. Partitions can have dedicated or shared processor resources. With shared resources, PowerVM can automatically adjust pooled processor resources across multiple operating systems, borrowing processing power from idle partitions to handle high transaction volumes in other partitions.

This very powerful approach to partitioning maximizes partitioning flexibility and maintenance. In addition to enabling fine-grained resource allocation, these PowerVM capabilities provides all the servers in the Power Systems family the capability to individually assign or reassign any resource (processor core, memory segment, I/O slot) to any partition in any combination — or to dynamically share resources among multiple virtual machines.

In a logically partitioning architecture, all of the server memory is physically accessible to all the processor cores and all of the I/O devices in the system, regardless of physical placement of the memory or where the logical partition operates. The POWER Hypervisor is designed to ensure that *any* code running in a partition (operating systems and firmware) only has access to the physical memory allocated to the dynamic logical partition. Power Systems models also have IBM-designed PCI-to-PCI bridges that enable the POWER Hypervisor to restrict DMA (Direct Memory Access) from I/O devices to memory owned by the partition using the device. The single memory cache coherency domain design is a key requirement for delivering the highest levels of SMP performance. Since it is IBM's strategy to deliver hundreds of dynamically configurable logical partitions, allowing improved system utilization and reducing overall computing costs, these servers must be designed to avoid or minimize conditions that would cause a full server outage.

IBM's availability architecture provides a high level of protection to the individual components making up the memory coherence domain; including the memory, caches, and fabric bus. It also offers advanced techniques designed to help contain failures in the coherency domain to a subset of the server. Through careful design, in many cases failures are contained to a component or to a partition, despite the shared hardware system design. Many of these techniques are described in this document.

Not only does this architecture allow exceptional configuration flexibility, it delivers capabilities not available in other, less flexible, architectures. Because processors, and processor cycles, can be dynamically reassigned between logical partitions, *processor sparing* includes not only reassigning full processor cores but also reassigning cycles (performance) between partitions helping to avoid outages when extra (spare) cores are not available.

By definition, Alternate Processor Recovery requires spare resource (equal to a core) if workload is to be moved from a failed processor. The Predictive Processor Deallocation technique also includes the ability to use a spare core ensure that partitions continue to operate without loss of performance.

Leveraging virtualization, the system takes an expansive view when defining a "spare" core. With PowerVM, a Power Server has considerable flexibility in collecting unused resources, even fractions of processing capacity, to create the "spare."

Finding spare capacity, in priority order:

• An unlicensed Capacity on Demand (CoD) core. The most obvious spare core in a system is one that is currently unlicensed in the system – one held in reserve for future use. This unlicensed core can be used to automatically "back-fill" for the deallocated bad processor core. In most cases, this operation is transparent to the system administrator and to end users, and the server continues normal operation with full functionality and performance. CoD sparing does not require an additional license and does not impact subsequent core licensing when the system is repaired.

This approach has some key advantages:

- 1. the spare can come from anywhere in the system, it need not be in the same physical enclosure or partition as the failing core and

- 2. a single spare is sufficient to allow for a deallocation event anywhere within the entire server.

- *If no CoD processor core is available*, the POWER Hypervisor attempts to identify an un-allocated licensed core somewhere in the system. This licensed core will be substituted and the failing CPU deallocated.

- If no spare processor core is available, the POWER Hypervisor attempts to identify a full core processor capacity equivalent from a shared processor pool (when enabled) a capability enabled by logical partitioning, because resources can be shared anywhere and redistributes the workload. In this case, the POWER Hypervisor reduces the allocation of processing resources given to partitions to account for the loss of a processor. This can be done at the granularity of a fraction of a processor.

- If the requisite spare capacity is not available, such as when the partitions in aggregate require more processing resources than would be available when a processor is deallocated, or if a shared processor pool is not used.

- 1. Predictive Processor Deallocation:

- Shared pool partitions: a core will not be deallocated until the next server reboot.

- Dedicated processor partitions: core deallocation will proceed (2 or more cores in partition) but no sparing will occur. In a uniprocessor partition, no core is deallocation until server reboot.

- 2. Alternate Processor Recover: At least one partition will be terminated not necessarily the one using the unreliable core. Core selection is determined by the POWER Hypervisor using Partition Availability Priority.

#### Partition Availability Priority

Power Systems give users the ability to prioritize partitions in advance. When partition availability priorities are specified, the POWER Hypervisor is able to terminate a lower priority partition (or partitions if necessary) and use the now available compute resource to keep higher priority partitions active.

When partitions are prioritized, even in those instances in which a partition need not be terminated, the priorities guide the order of deallocation of fractional resources from processors.

#### Additional POWER7 Processor Core Recovery Design Attributes

#### Level 1 Caches (Instruction and Data Cache Handling)

Instruction and data caches, typically considered part of a processor core, are designed so that detected errors are corrected, if necessary, by fetching faulty data or instructions from elsewhere in the memory hierarchy. The caches are organized into multiple data sets. If a persistent error is discovered in a set, the core can stop using that set — effectively repairing the problem. Multiple *set delete* events can also trigger Predictive Processor Deallocation, removing the bad cache (and core) before a catastrophic error is encountered.

Partition Availability Priority:

You can change the partition availability priority for the following partitions by first selecting one or more partitions and then choosing an availability priority from the field below the table. Please press OK button to submit your changes.

| Select                        | Partition Name | Partition Type | Processing units | Processing Mode | Availability priority |  |  |

|-------------------------------|----------------|----------------|------------------|-----------------|-----------------------|--|--|

|                               | Sys_Dump_1     | AIX or Linux   | 0                | Shared          | 127                   |  |  |

|                               | lpar4_RH_all   | AIX or Linux   | 0                | Shared          | 127                   |  |  |

|                               | lpar5_AIX_all  | AIX or Linux   | 0                | Shared          | 127                   |  |  |

|                               | lpar6_SuSe_all | AIX or Linux   | 0                | Shared          | 127                   |  |  |

|                               | lpar_1         | AIX or Linux   | 0                | Shared          | 63                    |  |  |

|                               | lpar_2         | AIX or Linux   | 2.0              | Shared          | 127                   |  |  |

|                               | lpar_3         | AIX or Linux   | 0                | Shared          | 127                   |  |  |

|                               | lpar_3a        | AIX or Linux   | 4.0              | Shared          | 127                   |  |  |

|                               | lpar_7         | AIX or Linux   | 0                | Shared          | 127                   |  |  |

| Availability priority: Update |                |                |                  |                 |                       |  |  |

OK Cancel Help

#### **Partition Availability Priority**

If Processor Instruction Retry does not successfully recover from a core error, the POWER Hypervisor will invoke Alternate Processor Recovery, using spare capacity (CoD or unallocated core resources) to move workloads dynamically. This technique can maintain uninterrupted application availability on a POWER6 processor-based server.

Should a spare core not be available, administrators can manage the impact of Alternate Processor Recovery by establishing a Partition Availability Priority. Set via HMC configuration screens, Partition Availability Priority is a numeric ranking (ranging from 0 to 255) for each partition.

Using this rating, the POWER Hypervisor takes performance from lower priority partitions (reducing their entitled capacity), or if required, stops lower priority partitions so that high priority applications can continue to operate normally.

Level 2 and Level 3 Caches

The level 2 and level 3 caches in the POWER7 processor use at least double error detect/single error correct (DED/SEC) ECC codes to ensure that a two bit error in any ECC word of data can be detected and that a single bit error in any ECC word can be corrected. This mechanism. when combined with the layout of the various bits of data within the ECC word provides primary protection against a soft error in either cache.

When data in a cache is read, errors are monitored by the

cache controller. If a set of cache data — a cache line — appears to have a persistent, correctable error, the cache controller will predictively deallocate the cache line through a procedure known as *cache line delete*.

In this process, the cache line is identified in the cache line directory as unavailable. Before the line is deleted, if any data from the cache needs to be written to memory, because it was modified in the cache, the data will be corrected using ECC and written to memory.

If, despite these precautions, data from a cache line is found to have an error that can not be corrected by ECC, then the cache line will still be deleted. If the data in the cache was unmodified, it will be "recovered" by fetching another copy from main memory. However, if the data in the cache line was modified in the cache, then the data will be written into main memory. Any faults that can be corrected by ECC will be corrected during the write. Any faults that can not be corrected will be identified as the data is stored by writing a special code into the ECC check bits of the words that were uncorrectable.

The firmware will not terminate any processes or partitions simply because an uncorrectable error was discovered. Instead, the use of the marked bad data will be monitored in the system through a process known as *Special Uncorrectable Error* handling. If the data is never used, computing will continue without interruption, however, if the data is used, in many cases the impact may be limited to just an application or partition termination.

An Uncorrectable data Error (UE) has potentially severe consequences. If a UE is encountered, the system firmware will request that the part containing the cache be replaced. However, if the fault is isolated to a single cache line, the cache line delete function is sufficient to prevent further problems associated with the error.

The L2 and L3 caches are controlled by much smaller arrays called directories which include information about the contents of particular cache lines. These directories are covered by a DED/SEC ECC code.

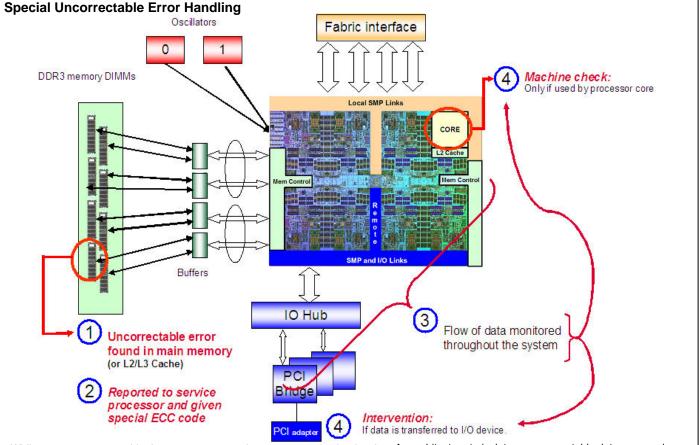

#### Special Uncorrectable Error Handling

While it's a rare occurrence, an uncorrectable data error can occur in memory or a cache despite all precautions built into the server. The goal of all Power Systems is to limit, to the least possible disruption, the impact of an uncorrectable error by using a well-defined strategy that begins with considering the data source.

Sometimes an uncorrectable error is transient in nature and occurs in data that can be recovered from another repository. For example: An L3 cache can hold an unmodified copy of data in a portion of main memory. In this case, an uncorrectable error in the L3 cache would simply trigger a "reload" of a cache line from main memory. This capability is also available in the L2 cache.

For cases where the data cannot be recovered from another source, a technique called Special Uncorrectable Error (SUE) handling is used. A SUE can be detected a number of ways:

1. ECC words containing uncorrectable errors in Level 2 and Level 3 caches will eventually be written to memory with a Special Uncorrectable Error (SUE) code indicating that the data is not reliable.

2. Faults in other parts of the system, such as main memory, can also cause data words to be marked with the SUE code.

This code indicates that an uncorrectable error has been identified at the data source and that the data in the "standard" ECC word is no longer valid. The check hardware also signals the service processor and identifies the source of the error. The service processor initiates actions to identify the component(s) containing the fault so that they will be called out for repair. The service processor also takes appropriate action to handle the error.

Simply detecting an error does not automatically cause termination of a system or partition. Rather, the

While rare, an uncorrectable data error can occur in memory or a cache despite An architecture to isolate an uncorrectable data error and all precautions built into the server. For cases where the data cannot be recovered from another source, a technique called Special Uncorrectable Error (SUE) handling is used. This code indicates that an uncorrectable error has been identified at the data source and that the data in the "standard" ECC word is no longer valid.

Simply detecting an error does not automatically cause termination of a system or partition. Rather, the use of the data is monitored throughout the system. If, as may sometimes be the case, the data is never actually used, but is simply discarded before it is loaded into a processor core or sent to an I/O device, then the error condition is voided and the system will continue to operate normally.

If a process attempts to use the data, the OS (AIX or Linux) is informed of the error and terminates only the specific user program. If the data is sent, via DMA, to an I/O controller, the system will "freeze" the GX adapter. This results in the loss of all I/O operations on that adapter. A properly configured server (with I/O redundancy) could avoid an outage. It is only in the case where the corrupt data is used by the POWER Hypervisor, and POWER Hypervisor Mirrored Memory is not used, that the entire system must be rebooted to preserve system integrity.

minimize its' system impact

- For uncorrectable errors in memory or cache

- No system impact if data is not used

- If used by a processor, the impact depends on what the processor is running

- If partition data ✓ Failure limited to a partition or less

- If POWER Hypervisor

- ✓ All partitions terminated

- ✓ No failure if Mirrored Hypervisor Memory used

- If the data is an I/O transfer (DMA) then I/O devices attached to the GX controller will be frozen

- May result in loss of partitions using the I/O if the I/O is critical and no redundancy is available.

use of the data is monitored throughout the system. If, as may sometimes be the case, the data is never actually used, but is simply discarded before it is loaded into a processor core or sent to an I/O device, then the error condition can safely be voided and the system will continue to operate normally.

If processor core tries to load the bad data, however, the request causes generation of a synchronous machine check interrupt. The firmware provides a pointer to the instruction that referred to the corrupt data. This data is often useful in mitigating the problem:

- 1. If the referenced data is owned by a user application (user space code), the operating system (currently supported versions of AIX and Linux) has the option of just terminating the application owning the data. If the data is operating system kernel data, then the partition will typically be terminated, but the rest of the system can continue to operate.

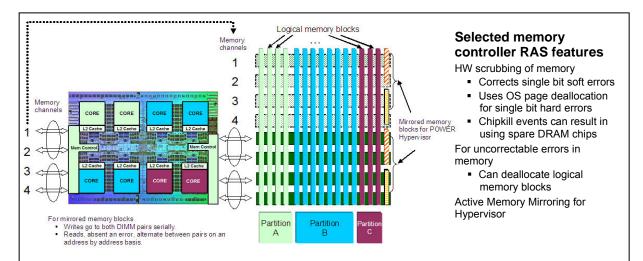

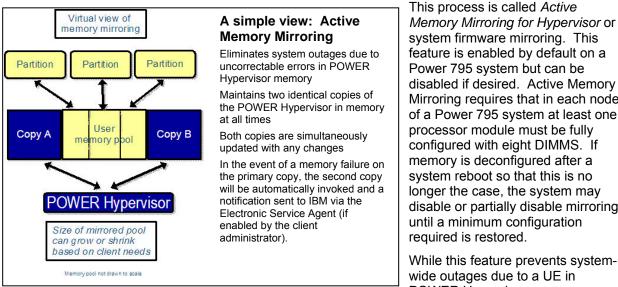

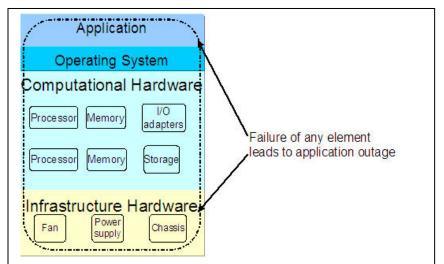

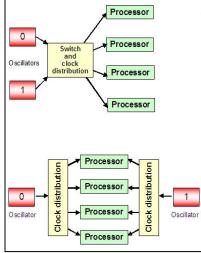

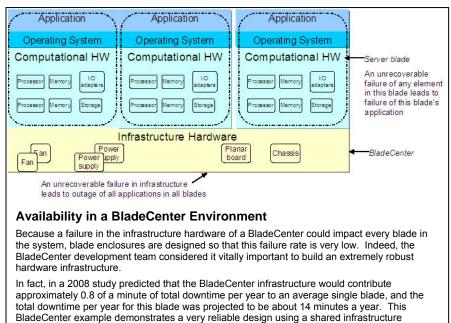

- Only in the case where the corrupt data is owned by the POWER Hypervisor, or in a critical area of POWER Hypervisor memory, would the entire system be terminated and automatically rebooted, preserving overall system integrity.