## Session G01

IBM System z9 109: Processor, Memory and System Structure

Harv Emery, IBM, Washington Systems Center

zSeries® EXPO FEATURING Z/OS, Z/VM, Z/VSE AND LINUX ON ZSERIES

September 19 - 23, 2005

San Francisco, CA

8/14/2005

#### **Trademarks**

The following are trademarks of the International Business Machines Corporation in the United States and/or other countries.

e-business logo\* ESCON\* RACF\* Resource Link HiperSockets Hypervisor System z9 z/Architecture IBM eServer IBM logo\*

On Demand Business logo

The following are trademarks or registered trademarks of other companies. Java and all Java-related trademarks and logos are trademarks of Sun Microsystems, Inc., in the United States and other countries.

Linux is a trademark of Linus Torvalds in the United States, other countries, or both.

UNIX is a registered trademark of The Open Group in the United States and other countries

Microsoft, Windows and Windows NT are registered trademarks of Microsoft Corporation in the United States, other countries or both.

SET and Secure Electronic Transaction are trademarks owned by SET Secure Electronic Transaction LLC. \* All other products may be trademarks or registered trademarks of their respective companies

zSeries\*

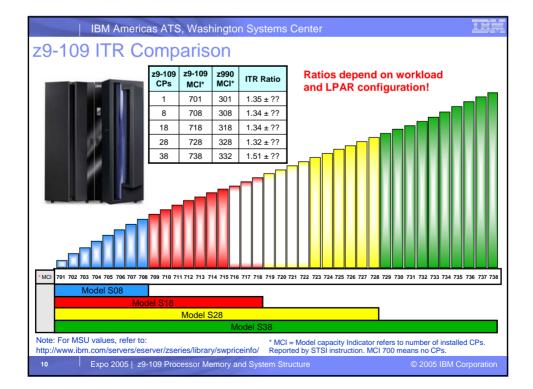

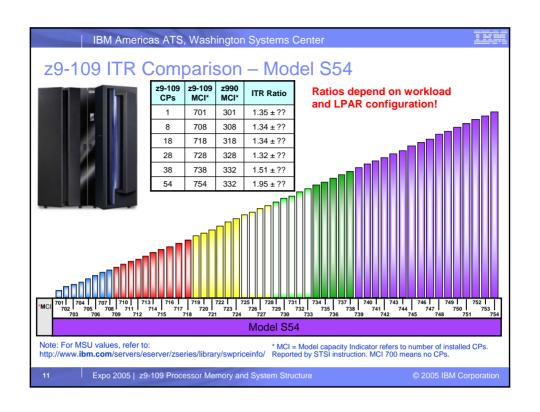

Performance is in Internal Throughput Rate (ITR) ratio based on measurements and projections using standard IBM benchmarks in a controlled environment. The actual throughput that any user will experience will vary depending upon considerations such as the amount of multiprogramming in the user's job stream, the I/O configuration, the storage configuration, and the workload processes. Therefore, no assurance can be given that an individual user will achieve throughput improvement/quident to the performance ratios stated here.

IBM hardware products are manufactured from new parts, or new and serviceable used parts. Regardless, our warranty terms apply.

All customer examples cited or described in this presentation are presented as illustrations of the manner in which some customers have used IBM products and the results they may have achieved. Actual environmental costs and performance characteristics will vary depending on individual customer configurations and conditions.

This publication was produced in the United States. IBM may not offer the products, services or features discussed in this document in other countries, and the information may be subject to change without notice. Consult your local IBM business contact for information on the product or services available in your area.

All statements regarding IBM's future direction and intent are subject to change or withdrawal without notice, and represent goals and objectives only.

Information about non-IBM products is obtained from the manufacturers of those products or their published announcements. IBM has not tested those products and cannot confirm the performance, compatibility, or any other claims related to non-IBM products. Questions on the capabilities of non-IBM products should be addressed to the suppliers of those products. Prices subject to change without notice. Contact your IBM representative or Business Partner for the most current pricing in your geography.

Expo 2005 | z9-109 Processor Memory and System Structure

IBM Americas ATS, Washington Systems Center

# Agenda

- IBM System z9<sup>™</sup> 109 (z9-109) Introduction

- System Structure

- Model Configurations and Memory

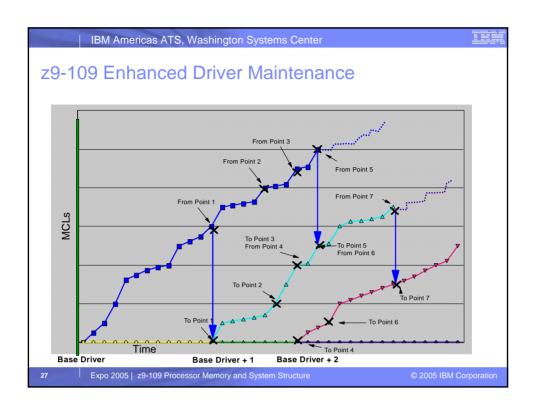

- Enhanced Driver Maintenance

- Processor Unit Specifics

- "On Demand"

- Cryptography and Security

<sup>\*</sup> Registered trademarks of IBM Corporation

#### IBM Americas ATS, Washington Systems Center

# IBM System z9™ Key Dates

#### z9-109 Announce – July 26, 2005

- First Day Orders

- Resource Link™ support available

- SAPR Guide and SA Confirmation available

#### Availability dates

- z9-109 Models S08, S18, S28 and S38: September 16, 2005

- Models S08, S18, S28, S38 CBU and On/Off CoD Activate: September 16, 2005

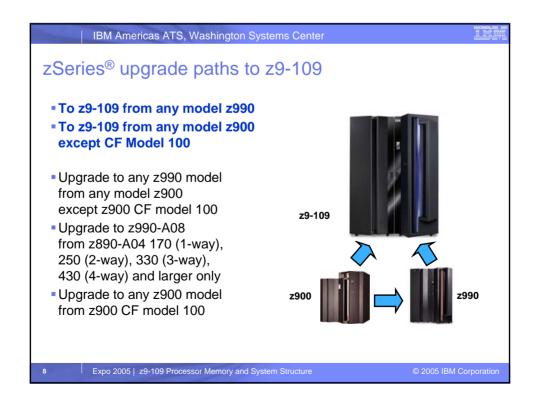

- z990 upgrades to z9-109 Models S08, S18, S28 or S38: September 16, 2005

- z900 upgrades to z9-109 Models S08, S18, S28 or S38: September 16, 2005

- z9-109 Model S54: November 18, 2005

- Model S54 CBU and On/Off CoD Activate: November 18, 2005

- z990 upgrades to z9-109 Model S54: November 18, 2005

- z900 upgrades to z9-109 Model S54: November 18, 2005

- Models S08, S18, S28 and S38 MES feature upgrades: December 16, 2005

- Model S54 MES feature upgrades: February 25, 2006

- Model S08, S18, S28 or S38 upgrade to Model S54: February 25, 2006

Expo 2005 | z9-109 Processor Memory and System Structure

© 2005 IBM Corporation

IBM System z9 109 Model Configurations and Memory

**ENABLING BUSINESS.** A THROUGH Z.

Expo 2005 | z9-109 Processor Memory and System Structure

#### IBM Americas ATS, Washington Systems Center

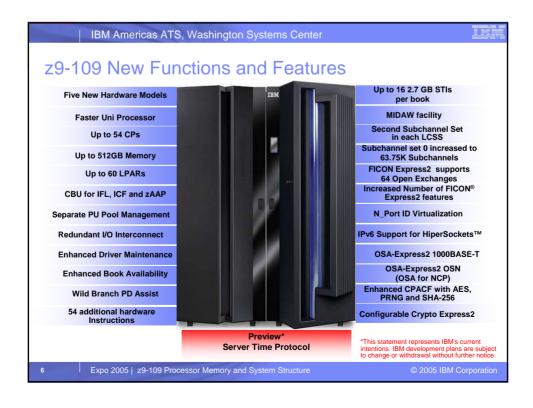

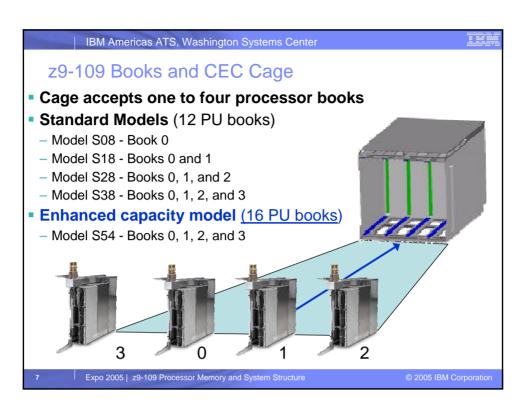

# z9-109 Model Configuration Overview

| Model                                    | S08      | S18      | S28      | S38      | S54      |

|------------------------------------------|----------|----------|----------|----------|----------|

| Books                                    | 1        | 2        | 3        | 4        | 4        |

| Processor Units (PUs)                    | 12       | 24       | 36       | 48       | 64       |

| Spare PUs                                | 2        | 2        | 2        | 2        | 2        |

| Standard SAPs                            | 2        | 4        | 6        | 8        | 8        |

| Configurable PUs<br>(Standard)           | 8        | 18       | 28       | 38       | 54       |

| Configurable PUs (Enhanced Availability) | NA       | 8        | 18       | 28       | 40       |

| GB Memory (Standard)                     | 16 - 128 | 16 - 256 | 16 - 384 | 16 - 512 | 16 - 512 |

| GB Memory (Flexible)                     | NA       | 32 - 128 | 32 - 256 | 32 - 384 | 32 - 384 |

| Maximum Channels                         | 960      | 1024     | 1024     | 1024     | 1024     |

Notes: Books with 16 PUs are available only in the Enhanced Capacity Model S54 Shaded boxes represent improvements compared to z990.

"Enhanced Availability" and "Flexible" configurations best exploit Enhanced Book Availability, the capability to run with one book removed from the configuration. Channel maximums vary by type. "Maximum Channels" assumes all ESCON.

#### z9-109 - Enhanced Availability Configurations

- Design Concept: Configure enough physical memory and limit PUs configured so that all active purchased PUs and memory remain available with one book removed from the configuration with Enhanced Book Availability

- Book removed concurrently for physical upgrade or repair

- Restart with a fenced book following the rare event of a book failure

- How?

- Select an S18, S28, S38, or S54 Model

- Configure no more than the following number of PUs

- 8 active PUs on the S18

- 18 active PUs on the S28

- 28 active PUs on the S38

- 40 active PUs on the S54

- Requires no special feature codes for PU or model configuration.

- Select Flexible Memory configuration features

21

Expo 2005 | z9-109 Processor Memory and System Structure

© 2005 IBM Corporation

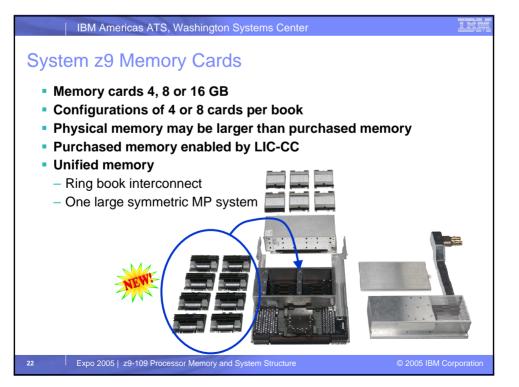

# z9-109 Memory Configurations

- Standard Lower cost: split memory as equally as possible among books, use smallest possible cards for purchased memory

- Flexible Supports Enhanced Book Availability: split memory as equally as possible among books, use large enough cards to ensure purchased memory remains available if any one book is removed

- Memory Purchase Increment 16 GB standard or flexible

| Purchased     | Model   | S08    | S18    | S28    | S38, S54 |

|---------------|---------|--------|--------|--------|----------|

| Standard      | Minimum | 16 GB  | 16 GB  | 16 GB  | 16 GB    |

| Configuration | Maximum | 128 GB | 256 GB | 384 GB | 512 GB   |

| Flexible      | Minimum | NA     | 32 GB  | 32 GB  | 32 GB    |

| Configuration | Maximum | NA     | 128 GB | 256 GB | 384 GB   |

| Purchased<br>memory:<br>Model S08 | 16 GB | 32 GB | 48GB  | 64 GB | 80 GB  | 96 GB  | 112 GB | 128 GB |

|-----------------------------------|-------|-------|-------|-------|--------|--------|--------|--------|

| Memory Card<br>Configuration      | 4 x 4 | 4 x 8 | 8 x 8 | 8 x 8 | 8 x 16 | 8 x 16 | 8 x 16 | 8 x 16 |

Expo 2005 | z9-109 Processor Memory and System Structure

© 2005 IBM Corporation

IBM Americas ATS, Washington Systems Center

# z9-109 Concurrent Memory Upgrades

- LIC enable additional memory to the physical limit of the installed cards and memory configuration

- Designed to be possible and concurrent in many but not all configurations

- Concurrent Book Add with additional memory

- Designed to be possible except for Models S38 and S54

- Exploit Enhanced Book Availability to change memory card configuration in existing books

- Not possible on Model S08

- Exploits capability for concurrent book remove, upgrade and return

- Designed to be possible with flexible memory and PU configurations

- May be possible with standard memory and PU configurations depending on LPAR configuration with appropriate planning and operator action

Note: Concurrent memory upgrades above are designed not to require CEC activation (POR).  $z/OS^{\circ}$  with "reserved memory" configured in the LPAR profile can add memory to a running partition. Otherwise adding memory to a partition requires deactivation, profile change and activation of the partition, which is designed to be disruptive to that partition only.

## z9-109 Model and I/O MES Upgrades

- Model upgrades

- Designed to be concurrent to Model S18, S28, and S38 from any lower z9-109 model by exploiting Concurrent Book Add

- Disruptive upgrade to Model S54

- All four books must be replaced with 16 PU books

- I/O cage add

- Disruptive

- Avoid by using "Plan Ahead" on initial order to configure additional cages for later requirements

- I/O and crypto feature adds

- Designed to be concurrent

- I/O add requires z/OS or z/VM<sup>®</sup> exploitation of dynamic I/O to avoid disruption.

- Concurrent exploitation of added cryptographic features requires "candidate" predefinition in the LPAR image profile.

25

Expo 2005 | z9-109 Processor Memory and System Structure

© 2005 IBM Corporation

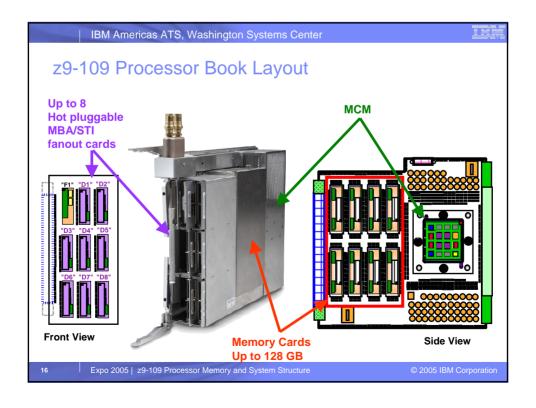

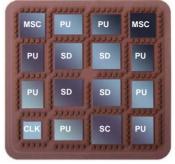

## z9-109 multi-chip module (MCM)

- Advanced 95mm x 95mm MCM

- -102 Glass Ceramic layers

- -16 chip sites, 217 capacitors

- -540 m of internal wiring

#### CMOS 10K chip Technology

- PU, SC, SD and MSC chips

- Copper interconnections, 10 copper layers

- 8 PU chips/MCM

- 15.78 mm x 11.84 mm

- 121 million transistors/chip

- · L1 cache/PU

- 256 KB I-cache

- 256 KB D-cache

0.58 ns Cycle Time

- 4 System Data (SD) cache chips/MCM

- 15.66 mm x 15.40mm

- 660 million transistors/chip

- L2 cache per Book: 40 MB

- One Storage Control (SC) chip

- 16.41mm x 16.41mm

- 162 million transistors

- L2 cache crosspoint switch

- L2 access rings to/from other MCMs

- Two Memory Storage Control (MSC) chips

- 14.31 mm x 14.31 mm

- 24 million transistors/chip

- Memory cards (L3) interface to L2

- L2 access to/from MBAs (off MCM)

One Clock (CLK) chip CMOS 8S

- Clock and ETR Receiver

Expo 2005 | z9-109 Processor Memory and System Structure

© 2005 IBM Corporation

IBM Americas ATS, Washington Systems Center

## z9-109 PU Types and Characterization Features

- Central Processor (CP) Feature 7810

- Provides processing capacity for z/Architecture™ and ESA/390 instruction sets

- Can support ANY operating system, z/VM guest, or Coupling Facility

- z9-109 has Capacity Marker features NOT Unassigned CP features

- IBM System z9 Application Assist Processor (zAAP) Feature 7814

- Under z/OS only and only the Java Virtual Machine (JVM)

- Requires z/OS 1.6 or later

#### Integrated Facility for Linux™ (IFL) and Unassigned IFL – Feature 7811 and 7831

- Provides additional processing capacity exclusively for Linux on System z9 workloads

- Runs Linux on System z9 or z/VM Version 4 or Version 5 for Linux guests

- Internal Coupling Facility (ICF) Feature 7812

- Provides additional processing capacity exclusively for the execution of Coupling Facility Control Code (CFCC) in a CF LPAR

- System Assist Processors (SAPs)

- Standard and Optional SAPs (Feature 7813) do I/O processing in the channel subsystem

- Two standard SAPs are provided per System z9 book

- Optional SAPs are typically NOT needed except, sometimes for TPF

- Spare PUs Not orderable

- Two standard spares per z9-109 and all available (unassigned) PUs

- Support "Transparent Sparing" for other PU types

#### z9-109 Concurrent PU Feature Conversions

- Flexibility to meet changing business environments

- Decreasing the number of CP or IFL features is designed to be concurrent.

- Can be ordered by MES or by CIU. (No RPQ needed.)

- Like z990 and z890, z9-109 unassigned IFL capacity is recorded by Unassigned IFL features

- Unlike z990, z9-109 does NOT have Unassigned CP features

- Like z890, z9-109 unassigned CP capacity is recorded by a Capacity Marker feature

- PU type conversions shown below with Yes are designed to be concurrent

- Can be ordered by MES or CIU (No RPQ needed)

- Example: From z9-109 S08 with eight CPs, convert one CP to an IFL

- Note: CP feature conversions also change (increase or decrease) the Capacity Marker feature

| To From        | СР  | IFL | Unassigned<br>IFL | ICF |

|----------------|-----|-----|-------------------|-----|

| СР             | Х   | Yes | No                | Yes |

| IFL            | Yes | Х   | Yes               | Yes |

| Unassigned IFL | No  | Yes | х                 | No  |

| ICF            | Yes | Yes | No                | Х   |

Note: Customer planning and operator action are required to exploit.

Disruptive if ALL current PUs are converted to different types

May require individual LPAR disruption if dedicated PUs are converted.

31

Expo 2005 | z9-109 Processor Memory and System Structure

© 2005 IBM Corporation

IBM Americas ATS, Washington Systems Center

# PR/SM™ Hypervisor™ PU Dispatching "Pools'

- PU Pool Physical PUs to dispatch to online logical PUs

- z9-109 with 10 CPs, 1 ICF, 2 IFLs, and 3 zAAPs

- CP pool contains 10 CP engines

- ICF pool contains 1 ICF

- IFL pool contains 2 IFLs

- zAAP pool contains 3 zAAPs

- z/OS LPAR can have different initial CP and zAAP weights

- z990 with 10 CPs, 1 ICF, 2 IFLs, and 3 zAAPs

- CP pool contains 10 CP engines

- Specialty pool contains 6 engines ICFs, IFLs, zAAPs

- z/OS LPAR zAAP weight is set equal to the initial CP weight

IBM Americas ATS, Washington Systems Center

# z9-109 Capacity Upgrade on Demand

- CUoD is designed to support addition of processors and/or memory or concurrent type conversion among CPs, IFLs, and ICFs without disruption to workloads running on the machine - no power-off, power-on. Includes:

- Addition of CP, ICF, IFL and zAAP includes turning on (assigning) "Unassigned" IFL features

- LIC enabling additional 16 GB memory increments

- Concurrent z9-109 model upgrade (Concurrent Book Add)

- Concurrent z9-109 memory upgrade exploiting Enhanced Book Availability

- CUoD capabilities can be exploited by IBM ordered/installed MES upgrade

- Some CUoD capabilities can be exploited by customer controlled upgrades:

- Capacity Backup (CBU) temporary emergency upgrades

- Customer Initiated Upgrade (CIU) permanent upgrades

- On/Off Capacity on Demand (On/Off CoD) temporary on-demand upgrades

- Notes:

- 1. CUoD is built on a base of concurrent "hot-plug" maintenance

- 2. I/O feature adds and removes are also nondisruptive but not really "CUoD"

- 3. Customer planning and operator action are required to take full advantage of CUoD. To avoid a planned outage, it may be necessary to predefine LPAR profiles with "reserved" resource specified. It may also be necessary to use z/OS or z/VM dynamic I/O capabilities. In some cases, disruption of certain LPARs is required following a concurrent hardware change.

## Concurrent Upgrade - Customer Controlled

#### CBU – Capacity Backup - Temporary emergency capacity upgrade

- Non-disruptive temporary addition of CPs, zAAPs, IFLs and ICFs in an emergency situation

- CBU contract required to order CBU features and CBU LIC CC

- Customer (or IBM) activates upgrade for test or temporary emergency

- Non-disruptive downgrade required after test or recovery completed

#### CIU – Customer Initiated Upgrade - Express - Permanent upgrade

- Customer capability to order and install permanent upgrade

- CUoD capabilities NOT included:

- Upgrades requiring parts (e.g. I/O feature card add)

- · Channel upgrades by LIC enable of existing ports

- CIU feature ordered to initiate contract and administrative setup

- Customer orders and installs upgrade via Resource Link™ and IBM RSF

#### On/Off Capacity on Demand - Temporary upgrade

- Nondisruptive temporary addition of CPs, zAAPs, IFLs, and ICFs in any situation

- Upgrades requiring parts (e.g. I/O feature card add) not supported

- "Right to use" feature ordered to initiate contract and administrative setup

- Customer orders and installs upgrade via Resource Link and IBM RSF

- Nondisruptive removal when capacity is no longer wanted

Expo 2005 | z9-109 Processor Memory and System Structure

IBM Americas ATS, Washington Systems Center

# System z9 CBU Features

- CBU features are ordered using eConfig

- Features are: CBU CP. CBU zAAP. CBU IFL and CBU ICF

- Limitations:

- Active PUs plus CBU PUs cannot exceed configurable PUs

- Unassigned CP capacity and Unassigned IFL features do not limit CBU PUs

- MES addition of active PU features to the base may require removal of CBU PU features

- After activation, the number of zAAPs cannot exceed the "number of CPs" Note: "Number of CPs" includes base CPs, CBU CPs and unassigned CP capacity recorded by the system's Capacity Marker feature.

#### MES conversion among CBU PU types is concurrent

- Order using eConfig

| То       | CBU | CBU  | CBU | CBU |

|----------|-----|------|-----|-----|

| From     | CP  | zAAP | IFL | ICF |

| CBU CP   | Х   | Yes  | Yes | Yes |

| CBU zAAP | Yes | х    | Yes | Yes |

| CBU IFL  | Yes | Yes  | Х   | Yes |

| CBU ICF  | Yes | Yes  | Yes | х   |

# System z9 On/Off Capacity on Demand

- Prerequisite for use:

- Customer Initiated Upgrade (FC #9898) and On/Off CoD (FC #9896) "right-to-use feature"

- Signed CIU contract with specific Ts & Cs governing temporary capacity

- Order temporary capacity Resource Link

- Can at most add capacity equal to active permanent capacity of the same type

For example Go from 2 CPs to 4, 1 IFL to 2, or do both in the same order

(Note: CIU upgrades and CBU do NOT have the this restriction)

- PUs that have never been characterized can be activated as CPs, zAAPs, IFLs or ICFs

- Unassigned IFLs can be activated only as IFLs Price advantage on z9-109

- Unassigned CP capacity can be activated only as CPs Price advantage on z9-109

- Order is manufactured: A LIC record is established and staged to RETAIN

- Multiple orders to meet different customer requirements can be staged

- Orders remain on RETAIN for an extended period until:

- Downloaded and activated (Initiates billing except for the 24-hour test)

- · Customer cancels order

- Machine is no longer under warranty or IBM Maintenance Service Agreement

- · Change to Permanent PU and/or memory configurations invalidates order

- A record, once activated, has no expiration date

- On/Off CoD activation and CBU can coexist

- Must deactivate one function to activate the other one.

- CBU PUs configured do not reduce On/Off CoD temporary capacity orderable

Expo 2005 | z9-109 Processor Memory and System Structure

© 2005 IBM Corporation

IBM Americas ATS, Washington Systems Center

# System z9 and zSeries CIU and On/Off CoD

- Order CIU and CoD "right to use" features

- Qualification, contracting, and pricing

- Resource Link ID Authorization

- Customer CIU or On/Off CoD order or On/Off CoD test order (up to 24 hours)

- Configure upgrade on Resource Link

- Secondary Approval (Option)

- Resource Link communicates with Remote Support Facility (RSF) to stage order and prepare download

- Customer notified order ready

- Access Support Element (SE) using Hardware Management Console (HMC)

- "Perform Model Upgrade"

- Code obtained using RSF and installed on target machine

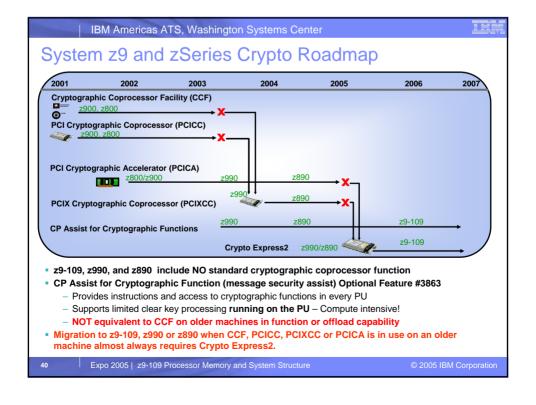

#### z9-109 CP Assist for Cryptographic Function (CPACF)

- High performance cryptographic instructions in every PU but NOT an offload engine

- Clear key cryptographic processing, hashing and random number generation

- Pseudo-optimized for low-latency SSL transactions

- Five capabilities, three System z9 exclusive:

- Advanced Encryption Standard (AES)

- 128 bit keys

- Secure Hashing 256 (SHA-256)

- Pseudo-random Number Generation (PRNG)

- Data Encryption Standard (DES) and Triple DES

- Up to 2\*\*64 byte message, interruptible execution

- Secure Hashing (SHA-1)

- CPACF Enabler Feature FC #3863

- No additional charge export control feature

- Required to enable AES, DES/TES, and PRNG (SHA-1 and SHA-256 are always enabled)

- Required to order Crypto Express2

- Recommended on EVERY system if allowed by law

Expo 2005 | z9-109 Processor Memory and System Structure

© 2005 IBM Corporation

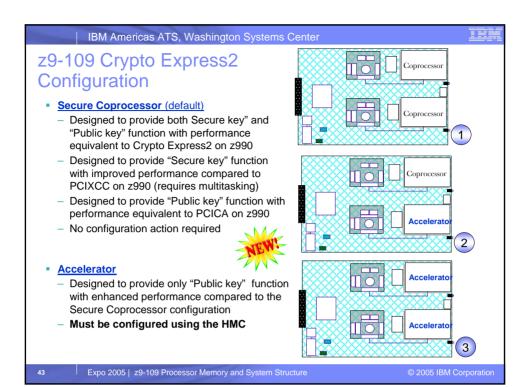

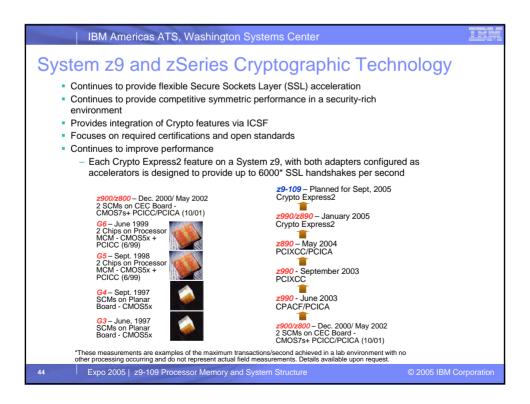

# System z9 Crypto Express2 Feature

- Dual Integrated Cryptographic Coprocessors

- Individually configurable as:

- Secure Coprocessor (default), designed to provide both "Secure key" and "Public key" function

- Accelerator, designed to provide only "Public key" function with enhanced performance

- Current applications expected to run without change

- Secure Coprocessor mode is fully programmable and supports User Defined Extensions (UDX)

- Scalable (no CP affinity)

- Supported Crypto Express2 configurations:0, 2, 3, 4, 5, 6, 7, or 8 features (but NOT 1 feature)

- Plugs into an I/O card slot (no external cables)

- Up to 8 Crypto Express2 features can plug into a single I/O cage

- Designed for FIPS 140-2 Level 4 Certification

- Trusted Key Entry (TKE) support (optional)

- If TKE configured, TKE 5 is required on z9-109

- Updated user interface compared to TKE 4.x

- Secure operational and master key loading

- Smart Card Reader support

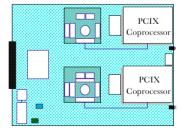

#### System z9 Trusted Key Entry (TKE) Workstation 5.0

- Optional TKE Workstation:

- The only TKE feature that supports z9-109

- Orderable on z9-109, z990, z890, z900 and z800

- TKE 5.0 LIC: FC 0855

- Requires TKE 5.0 hardware

- TKE 5.0 hardware: FC 0859

- Requires TKE 5.0 LIC

- xSeries-based system unit, keyboard, flat panel, mouse

- · PCI-X Crypto Coprocessor

- · Ethernet connectivity only

- Optional Smart Card Reader: FC 0887

- Optional Additional Smart Cards: FC 0888

- TKE 5.0 Hardware and LIC support to enter secure cryptographic keys for:

- z9-109: Crypto Express2

- z990 and z890: PCIXCC and Crypto Express2

- z900 and z800: CCF and PCICC

PCI-X Crypto Coprocessor

4

Expo 2005 | z9-109 Processor Memory and System Structure

© 2005 IBM Corporation

IBM Americas ATS, Washington Systems Center

# System z9 Security Certifications

- Cryptographic Security Certification

- Crypto Express2 Designed to meet FIPS 140-2 Level 4

- Smart Cards Certified to meet FIPS 140-2 Level 2

- Common Criteria (ISO/IEC 15408) Evaluation Assurance Levels Reference: <a href="http://niap.nist.gov/cc-scheme/">http://niap.nist.gov/cc-scheme/</a>

- z/OS 1.6 with RACF® Certified for Controlled Access Protection Profile (CAPP) EAL3+ and Labeled Security Protection Profile (LSPP) EAL3+

- SUSE LINUX SLES 8 Certified for Controlled Access Protection Profile (CAPP) EAL3+

- z/VM V5.1 with RACF for z/VM IBM has applied for Controlled Access Protection Profile (CAPP) EAL3+ and the Labeled Security Protection Profile (LSPP) EAL3+

- SOD: IBM intends to submit for evaluation z/VM V5.2 with the RACF® for z/VM for Controlled Access Protection Profile (CAPP) and the Labeled Security Protection Profile (LSPP) at EAL4