IBM Systems and Technology Group

## Silicon Technology Outlook

Dieter Wendel Distinguished Engineer IBM Deutschland Research & Development wendel@de.ibm.com

© 2014 IBM Corporation

#### IBM Deutschland Research & Development GmbH

8-968555 - 66926868-98

# Agenda

- Intro

- **CMOS Scaling**

- Lithography

- Device innovations

OF A CA

The third dimension

#### IBM Technologies.....

IBM zEnterprise Systems

#### IBM

## All build on sand

. . . . . . . . . .

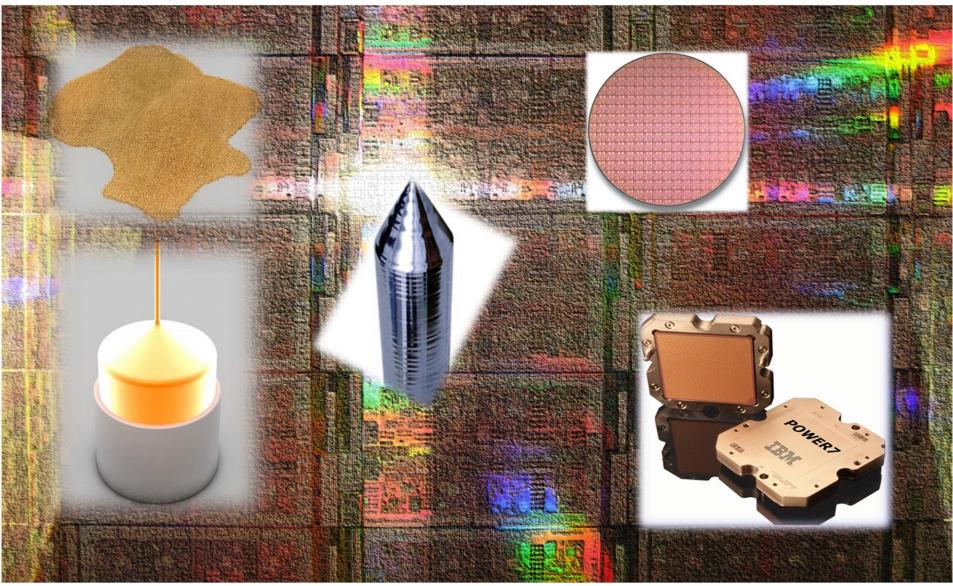

#### Fortunately we know how do turn sand into hardware

### It started different

## Konrad Zuse Z1

- First freely programmable computer using

- Boolean logic

- Binary floating point

- Build between 1936-1938 during WW II in Berlin

- Contained all parts of a modern computer

- Control unit

- Memory

- Micro sequences

- Floating point unit

- Two registers

- Technology: mechanical via metal sheets

- Driven by manually or optinal electrical motor from a vacuum cleaner Never worked flawlessly due to mechanical problems

Source: http://user.cs.tu-berlin.de/%7Ezuse/Konrad\_Zuse/en/rechner\_z1.html

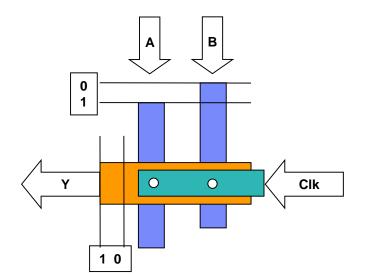

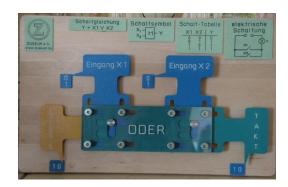

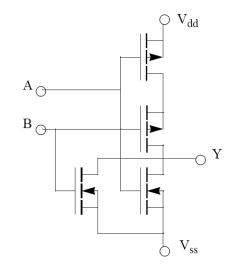

## Metal sheets vs CMOS transistors:

4 metal sheets to build a logic gate 2 inputs, 1 output, 1, clock" => 30000 metal sheets represent 7500 logic gates

4 CMOS transistors per logic gate CMOS needs two complementary pairs of CMOS transistors Six CMOS transistors for a single memory cell

#### IBM

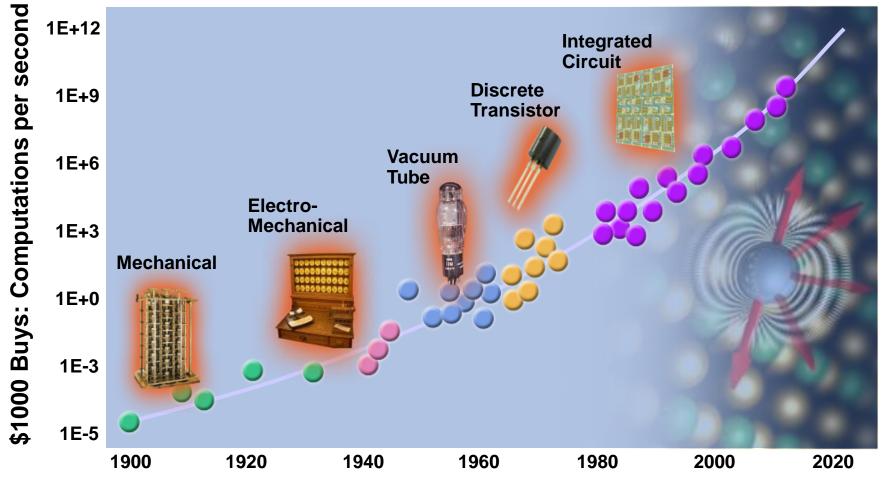

#### Moore's Law or What do a 1000 \$ buy?

Source: Kurzweil 1999 – Moravec 1998

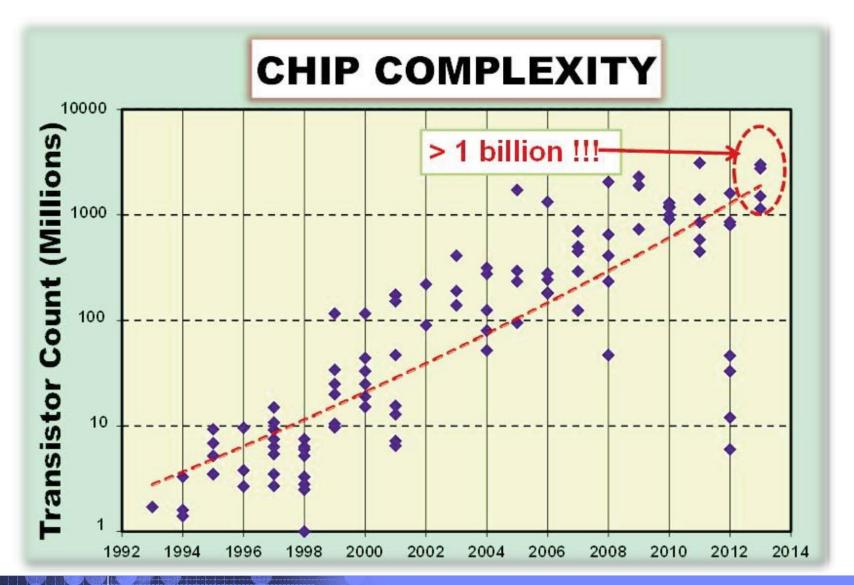

## **CMOS Scaling**

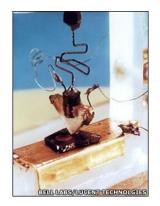

- Transistor (1947), Bardeen, Brattain & Shockley

- First integrated circuit (1959), Kilby

- Moore's Law (1965)

"*Cramming more components onto integrated circuits*" Complexity of chips doubles every 24 months

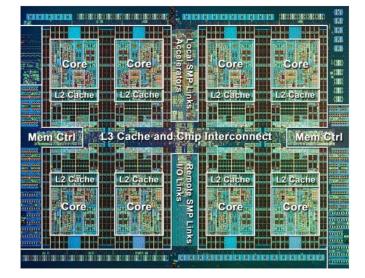

- Cell Processor (2005)

234 Million Transistors in 90nm Technology

- POWER 6 (2006)

790 Million Transistors in 65nm Technology

- POWER 7+ (2012)

2.1 Billion Transistors in 32nm Technology

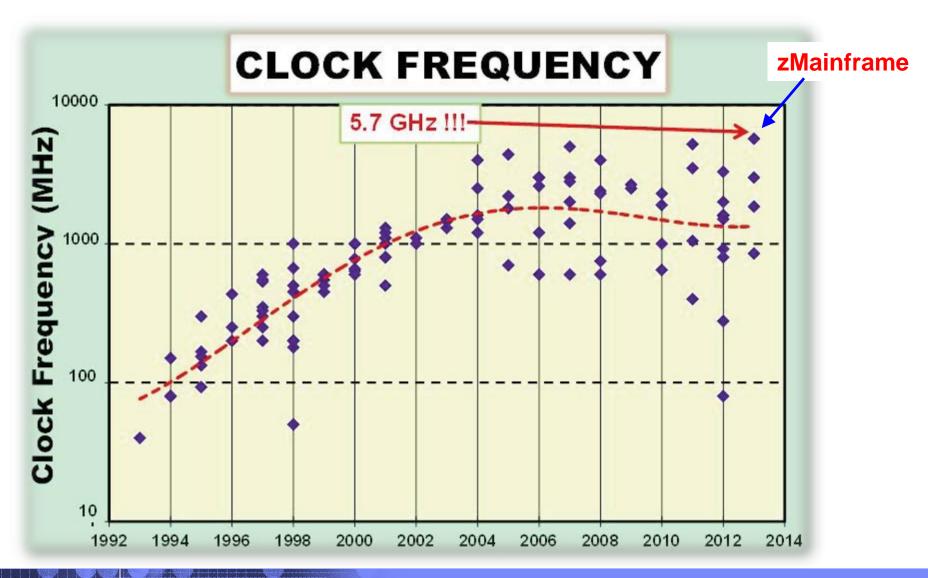

#### Trends Observed Across Industry (ISSCC 2013 Supplement)

© 2014 IBM Corporation

Trends Observed Across Industry (ISSCC 2013 Supplement)

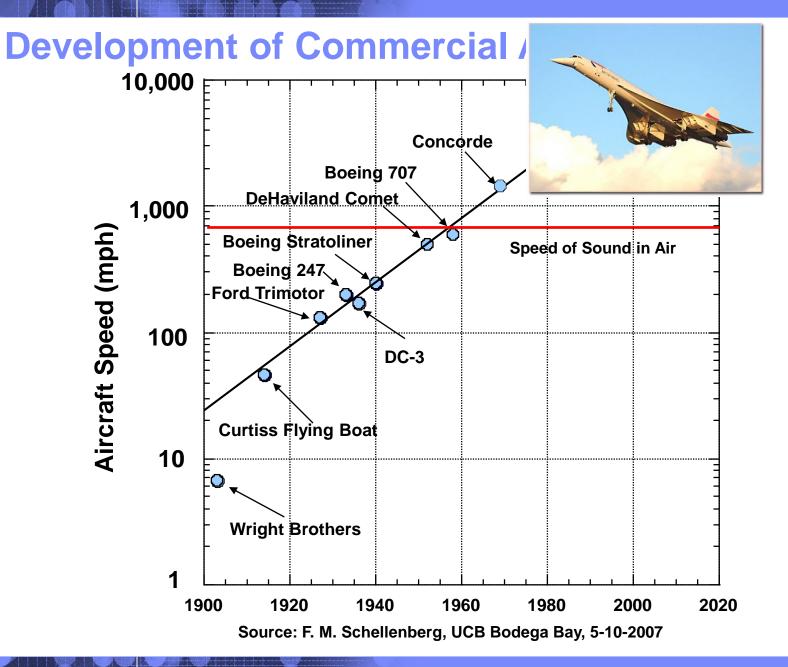

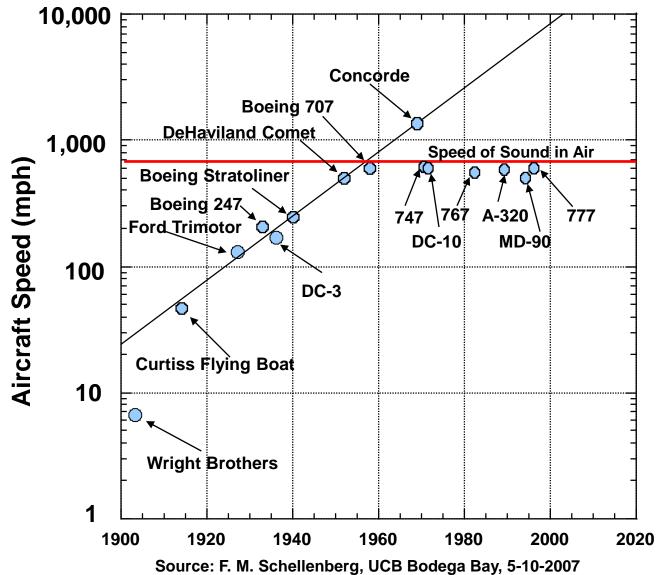

#### **Commercial Aviation**

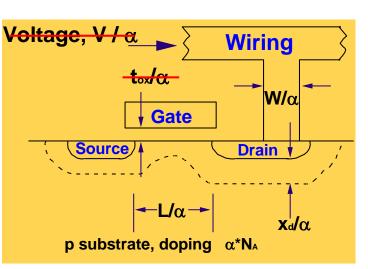

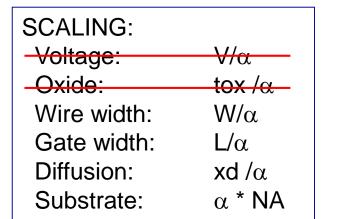

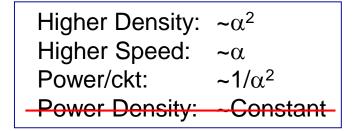

## Traditional CMOS Scaling (Dennard, 1974)

Channel Effects

•Drain Induced Barrier Lowering

Increasing loff

•Vt dependence on Vds

Sub-threshold slope

#### < 65 nm

| -                       |              |      | COVER |       |

|-------------------------|--------------|------|-------|-------|

| manners 6               | and a second | 10.0 | 100   |       |

|                         | -            |      |       | <br>_ |

|                         |              |      |       |       |

|                         |              |      |       |       |

| And a local data of the | 16           | -    | Gaine | 1000  |

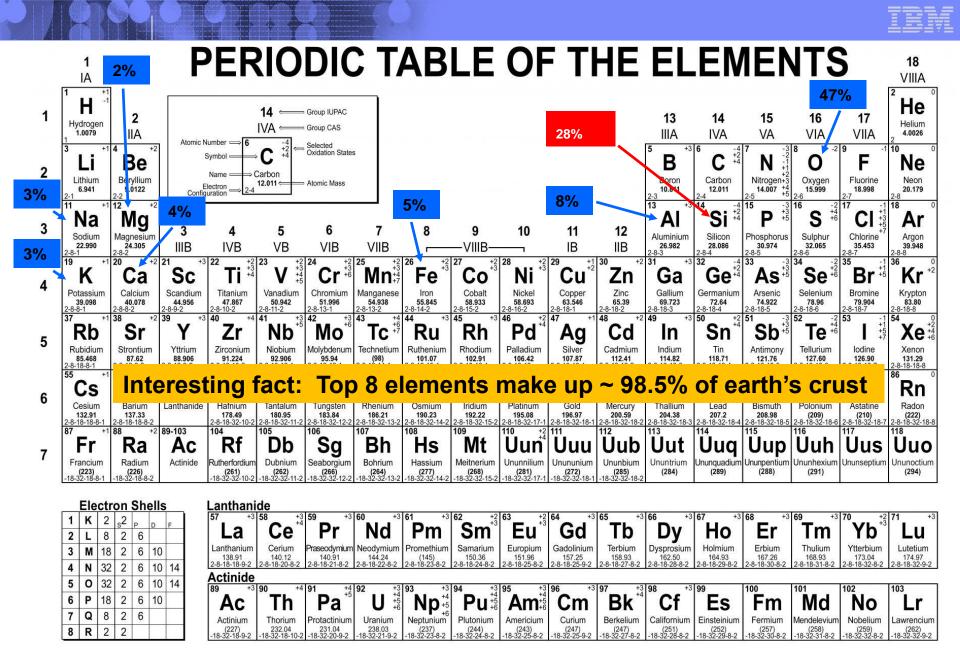

# **Improving Performance**

No longer possible by scaling alone

- New Device Structures

- New Device Design point

New Materials helium hydroger Before 90's 2 1 beryllium 4 neon 10 lithiun Since the 90's 3 boror carbor oxygen 6 Li Be 5 8 9 Ne 6.941 sodium 20.180 argon 18 9.0122 **Beyond 2006** sulfur 11 phosphoru aluminum silicon 16 agnesiu 12 Mg Na 13 14 15 S 17 Ar 22.990 potassiun 32.065 39.948 selenium krypton inganes galliun 19 calcium anadiu **2**5 26 zinc 31 arsenic Bromin 36 candi romiu cobalt nickel coppei 34 κ 20 Ca 21 Sc 22 Ti 23 V 24 Cr Mn Fe 27 28 29 30 Ga 32 33 Se 35 Kr Ge 55.845 39.098 rubidium 69.723 indium 54.938 78.96 tellurium 83.80 antimony 47 50 37 rhodiun 48 51 53 trontiun vttrium irconiu niobiur olvbden 43 utheniu palladiur 49 52 xenon Rb 39 40 42 43 45 Sb 54 38 41 45 Ag Cd Sn Te Тс In Sr 85.468 caesium 112.41 114.82 118,71 121.76 127.60 126.90 [98] lead 82 utetiur 71 thallium rador osmiur 76 gold 79 nercury poloniun astatine nafniur ngster 29 55 barium 57-70 Rheniur iridium olatinum 80 81 bismuth 84 85 86 73 Ta \* 75 Re тι Pb Cs 56 72 Hf Os 77 78 Hg 83 Po At Rn Au Lu w 132.91 franciun 174.97 190.23 196.97 204.38 207.2 ununquadi 200.59 erford aborgiu 106 bohrium 107 unununiun ununhiun 89-102 112 87 88 103 104 105 108 109 110 111 114 \*\* Rf Fr Ra Lr Db Sg Bh Hs Mt Uun Uuu Uub Uuq [289] [223] [226] [262] [261] [262 [264] [269] [271]

| *lanthanoids | lanthanium<br><b>57</b><br>La | cerium<br>58<br>Ce        | Praeseo<br>dymium<br><b>59</b><br>Pr | neodymium<br>60<br>Nd        | 61<br>Pm<br>[145]              |                         | europlum<br>63<br>Eu           | gadollinium<br>64<br>Gd     | terbium<br>65<br>Tb | dysprosiur<br>66<br>Dy           | holmium<br>67<br>Ho              | erbium<br>68<br>Er | thullium<br>69<br>Tm | ytterbium<br><b>70</b><br>Yb |

|--------------|-------------------------------|---------------------------|--------------------------------------|------------------------------|--------------------------------|-------------------------|--------------------------------|-----------------------------|---------------------|----------------------------------|----------------------------------|--------------------|----------------------|------------------------------|

| **actinoids  | actinium<br>89<br>AC          | 90<br><b>Th</b><br>232.04 | protactinium<br>91<br>Pa<br>231.04   | uranium<br>92<br>U<br>238.03 | neptunium<br>93<br>Np<br>[237] | 94<br>94<br>PU<br>[244] | americium<br>95<br>Am<br>[243] | ourium<br>96<br>Cm<br>[247] | 97<br>97<br>Bk      | californium<br>98<br>Cf<br>[251] | einsteinium<br>99<br>ES<br>12521 | 100                | 101<br>Md<br>[258]   | 102<br>NO<br>[259]           |

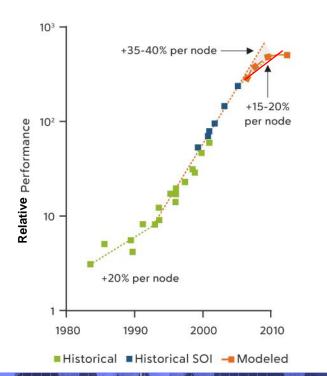

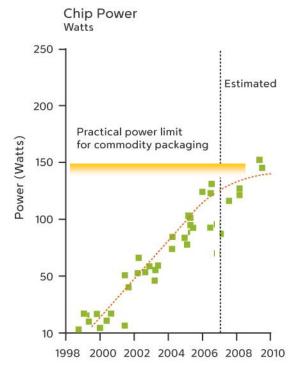

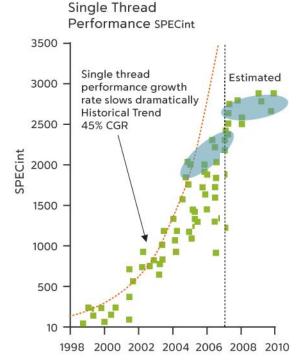

### CMOS Technology Trends

Conventional CMOS scaling benefits are diminishing.

Transistor performance scaling to continue, but at a slower rate

Power is limiting practical performance

#### Single thread performance growth is slowing dramatically

# Lithography

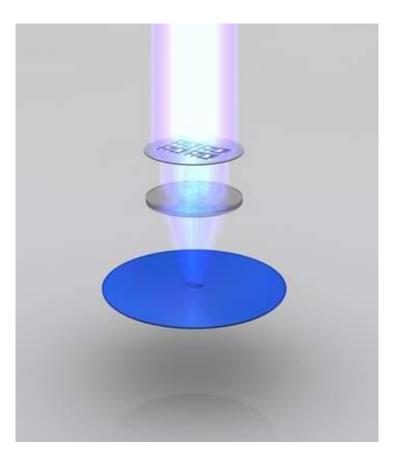

#### Pushing the Physical Limits of Optical Lithography

- Historically driven by lowering wavelength or increasing lens numerical aperture

- Immersion lithography with 193nm extended for five generation through 10 nm double patterning, implementation of restricted design rules, etc...

- EUV offers a return to single patterning with 13.5nm wavelength

- facing many delays in maturation (radiation source power output)

=> EUV still carries significant risk going forward

Technology Readiness (Year) / Node Name

🞽 Device Pitch 🛛 🗮 Wiring Pitch 🦳 Limit of Single Exposure 193i 🛛 🗖 Limit of Douple Patterning 193i

Lars Liebmann

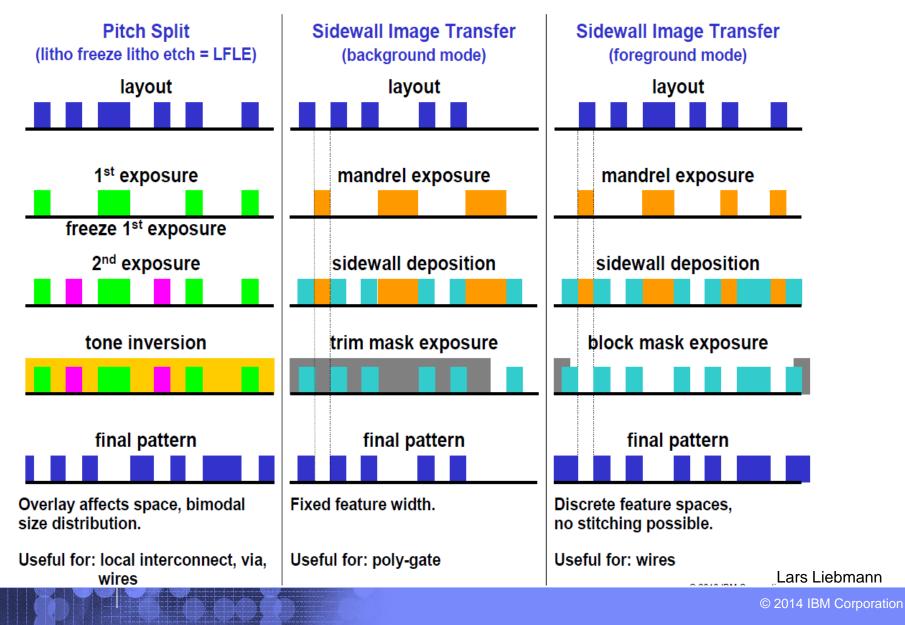

#### **Double pattern Variants**

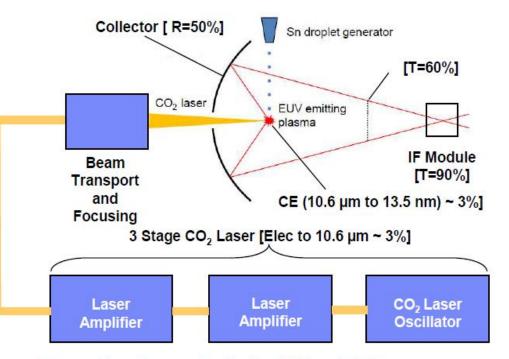

#### EUV: extreme ultra-violet lithography

#### ASML's exposure system

Cymer's EUV source

Conversion from wall plug to EUV: ~ 0.02%

Program is making steady progress.

Source power, resist line-edge roughness, mask-blank defects, optics lifetime, overall system cost... remain a challenge

Lars Liebmann

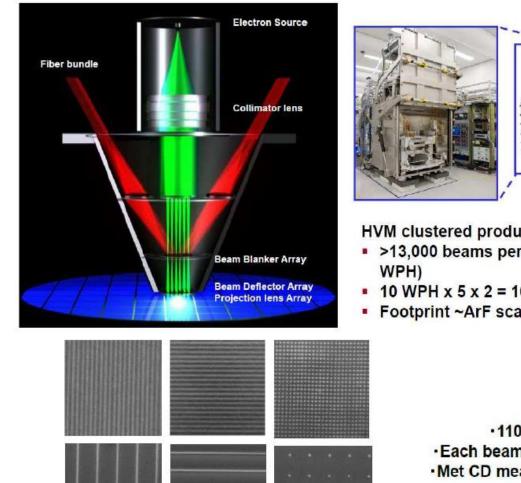

#### MAPPER: multiple e-beam mask-less lithography

HVM clustered production tool: >13,000 beams per chamber (10 10 WPH x 5 x 2 = 100 WPH

Footprint ~ArF scanner

110 beams working Each beam covers a 2x2µm<sup>2</sup> block Met CD mean-to-target & CDU spec

Multiple E-beam Decisions for 22nm and Sub-22nm Lithography, B.J. Lin tsmc, Inc. , Synopsys 2010 TechForum

Lars Liebmann

© 2014 IBM Corporation

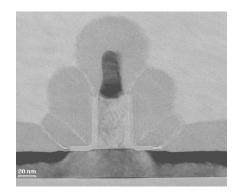

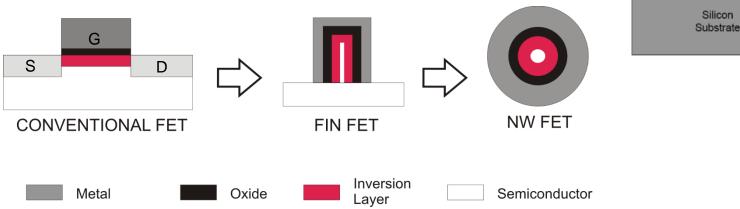

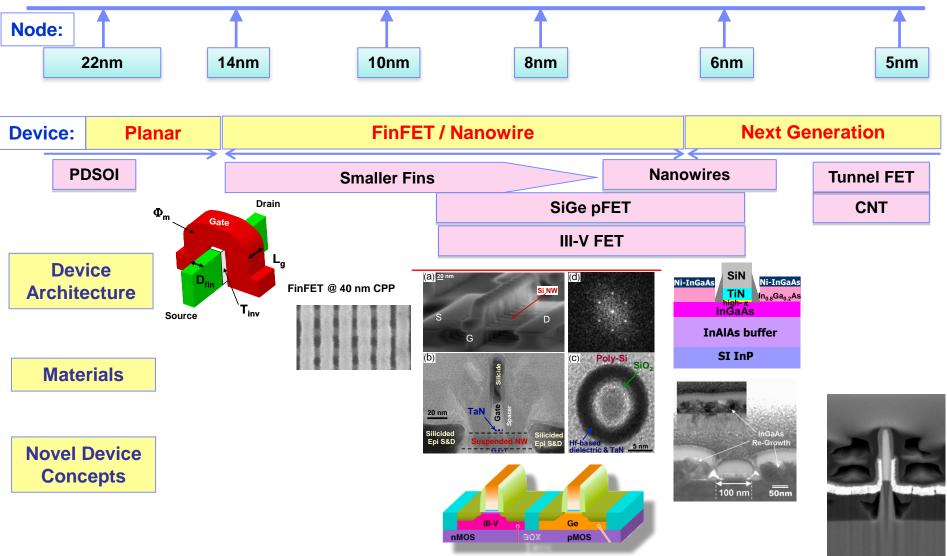

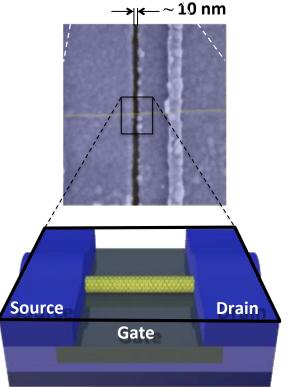

#### **Devices inovation**

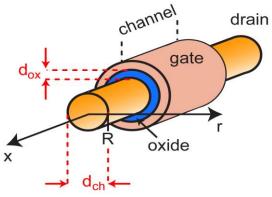

Electrostatic control of the channel depends on the gate architecture (gate control).

- Nanowire offers optimum electrostatic gate control of channel

- Improved scaling: L<sub>g</sub> ~1.5 diameter

- Reduced leakage current/power

Drain

Source

Gate

Oxide

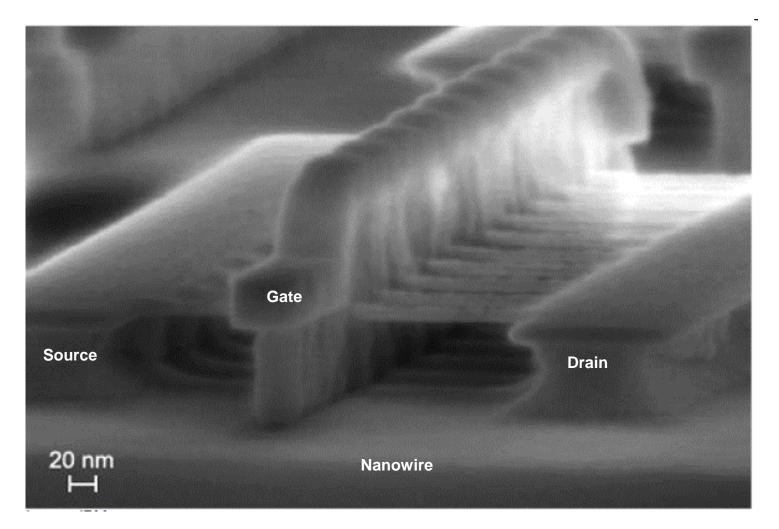

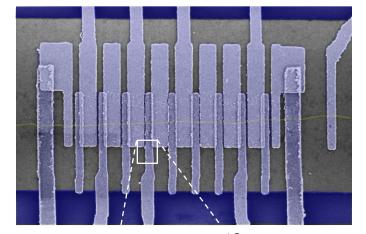

#### Silicon Nanowires, 5nm and beyond

#### **Potential device roadmap**

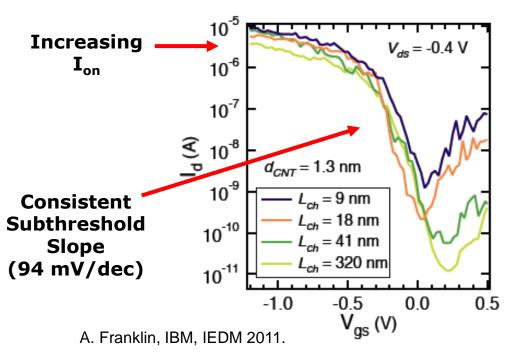

# Sub-10nm CNT FET

CNT devices with scaled channel length are fabricated on one CNT

- Channel length was scaled: 320 nm to 9 nm

- First demo of sub-10 nm channel CNT FET

- Minimal short channel effects into the sub-10nm channel length region

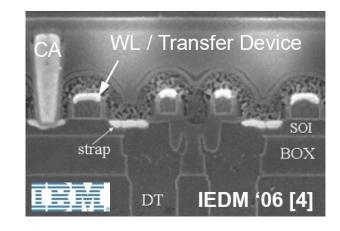

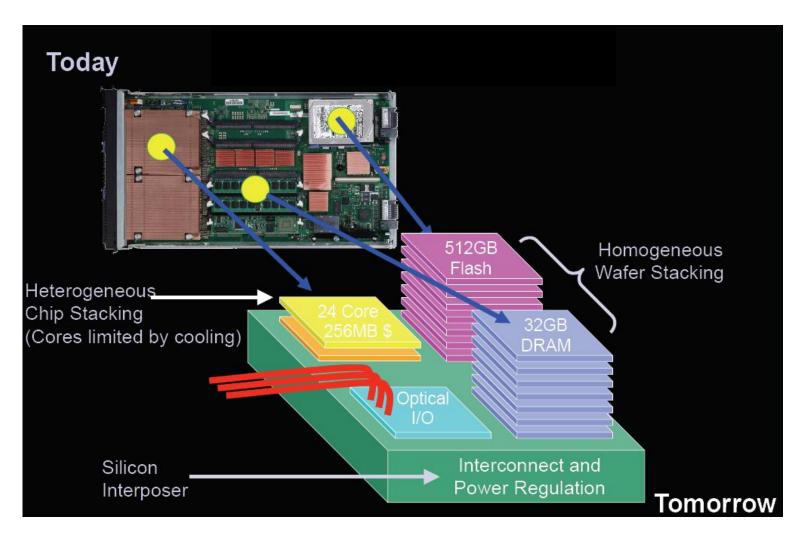

## **The Third Dimension**

Despite all innovative materials/structures CMOS scaling looses benefits

- Large chips => long wires

- Cache memory size limited => access time critical for performance

- Power-Management, -Delivery, -Distribution, -Dissipation

- I/O => Bandwidth, latency, on-chip integration

- Let's enter the 3rd dimension

Embedded DRAM on SOI, 2006

## **3D Chip Integration**

#### **Benefits**

- Density

- Memory access time

- Performance (Bandwidth, Latency)

- Heterogeneous components

#### Challenges

- Process

- 3D Design / EDA Tools

- Heat Dissipation, Hotspots

- Test

- Yield / Reliablity

| 1000000110 |     |      |      |      | - |

|------------|-----|------|------|------|---|

|            |     |      |      |      |   |

|            |     |      |      |      |   |

|            | -   |      | 1000 | 100  |   |

|            | 200 | 22.2 |      | 1000 |   |

| -          | 100 | _    |      |      |   |

|            |     |      |      |      |   |

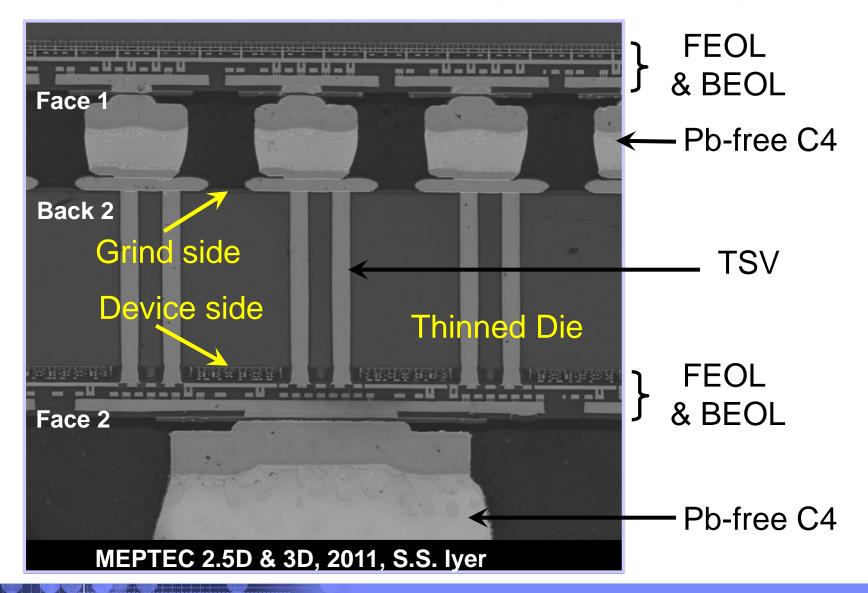

#### **3D Interconnect schemes**

Wire Bonding

• Coupled virtual connections (capacitive, inductive)

• Microbump (C4)

• Through Silicon Vias (TSV)

#### **Close up of 45 nm 3D module (Face to Back)**

## Hybrid Memory Cube **Hybrid Memory Cube** Microsoft Open-Silicon SK hynix ARM SAMSUNG EXILINX Micron **TSVs** Wide Data Path 16 x 32-bits High-Speed Link DRAM 2 x 64-bit SERDES Logic Chip

### **System on Silicon Interposer**

#### Barth et al, SRC 2011

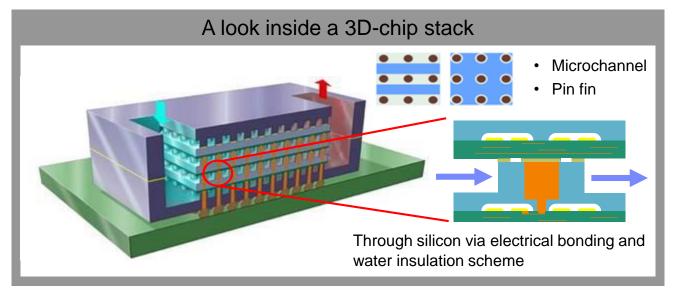

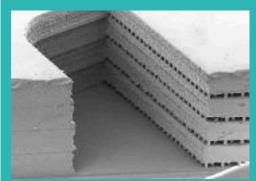

## **3D-chips cooled with interlayer liquid cooling**

#### B. Michel et al, CeBIT 2011

Exploit 3D to full extent => System in a Cube...

cross-section through fluid port and cavities

Test vehicle with fluid manifold and connection

## IBM System & Technology Group

Vielen Dank Thank You

Dieter Wendel wendel@de.ibm.com +49-7031-163019

### IBM System & Technology Group

Disclaimer

(c) Copyright International Business Machines Corporation 2010.

All Rights Reserved.

The following are trademarks of International Business Machines Corporation in the United States, or other countries, or both. IBM IBM Logo Power Architecture

Other company, product and service names may be trademarks or service marks of others.

All information contained in this document is subject to change without notice.

The products described in this document are NOT intended for use in applications such as implantation, life support, or other hazardous uses where malfunction could result in death, bodily injury, or catastrophic property damage. The information contained in this document does not affect or change IBM product specifications or warranties. Nothing in this document shall operate as an express or implied license or indemnity under the intellectual property rights of IBM or third parties. All information contained in this document was obtained in specific environments, and is presented as an illustration. The results obtained in other operating environments may vary.

While the information contained herein is believed to be accurate, such information is preliminary, and should not be relied upon for accuracy or completeness, and no representations or warranties of accuracy or completeness are made.

THE INFORMATION CONTAINED IN THIS DOCUMENT IS PROVIDED ON AN "AS IS" BASIS. In no event will IBM be liable for damages arising directly or indirectly from any use of the information contained in this document