# **Taking the Cross out of Cross Memory**

Address Spaces, Data Spaces & Access Registers (oh my!)

# NaSPA May 14th, 2019

Patty Little <u>plittle@us.ibm.com</u>

John Shebey <u>jshebey@us.ibm.com</u>

2018 IBM Corp SHARE St. Louis, August 2018

**⊚⊕**§∋

# **Trademarks**

The following are trademarks of the International Business Machines Corporation in the United States and/or other countries.

- ·MVS

- •OS/390®

- •z/Architecture®

- ·z/OS®

\* Registered trademarks of IBM Corporation

2018 IBM Corp

SHARE St. Louis, August 2018

ഭവ

### **Table of Contents** • WHY BE CROSS? • Isolation of programs and data ..... 6 • Asynchronous address space communication ...... 8 • CROSS MEMORY • What is cross memory? ..... 10 • Linkage Stacks ...... 26 SHARE St. Louis, August 2018 2018 IBM Corp

### **Table of Contents (continued)** • EXTENDED ADDRESSABILITY • Access registers in dump ...... 48 • Data space storage in dump ...... 50 • Applied example ..... 51 APPENDIX • Putting it together, with control registers ...... 58 • Identifying data spaces owned by ASID ...... 62 SHARE St. Louis, August 2018 2018 IBM Corp

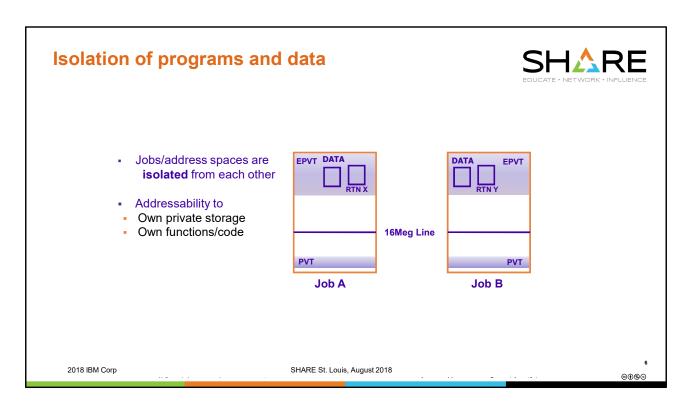

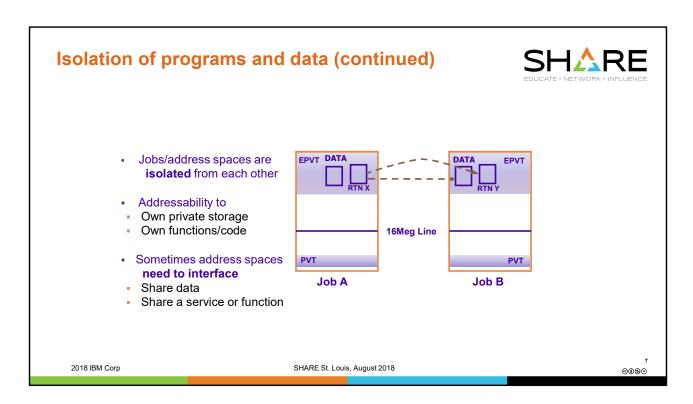

- \* Built into the design of z/OS is the protection that comes from isolating one address space from another. A job can only directly and easily access its own programs and data located within its private storage or in common (Nucleus and LPA, SQA and CSA). .

- \* An address space represents a function or application. Each function/application has its own data and its own code.

- \* The operating system intentionally isolates address spaces from each other. This is to provide protection of the address space's code and storage.

Cross memory services and instructions can be used to allow one function to access the data or code in another function. Various authorization checks must be passed before one address space can establish cross memory access to another address space.

The MVS Extended Addressability Guide is an excellent reference for discussion and examples of cross memory concepts.

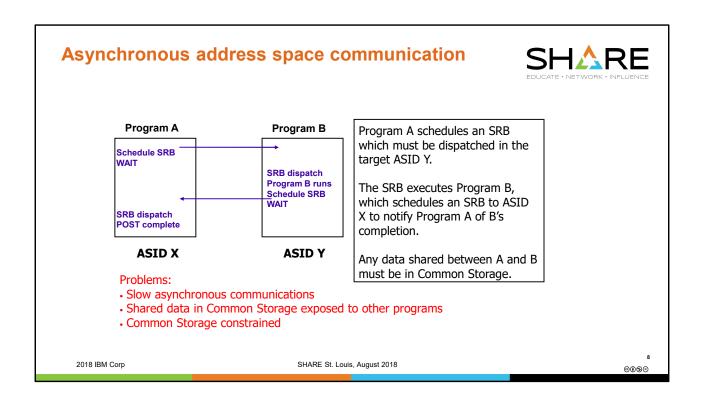

In the early days of MVS, a program could communicate with a program in another address space, but only through a cumbersome asynchronous method. If Program A, running in ASID X, needed a service or function that was performed by Program B in ASID Y, there was no way to directly call a program that resided in a different address space.

Program A solved this by scheduling an SRB to the target address space (Y) and then waiting to be notified of completion. The SRB would be queued and eventually dispatched in the target address space, ASID Y. The SRB would run program B, possibly also asynchronously by posting a task for Program B in ASID Y to run. Once Program B dispatched and ran, notification needed to be sent back to Program A. Another SRB was scheduled back to ASID X. This SRB would be queued and then dispatched, and would post Program A which was waiting for the notification. Finally, Program A, running under its task, would be dispatched and continue.

This asynchronous method required several trips through the MVS dispatcher and a wait/post mechanism to notify for completion. In addition, any data shared between the programs must be in Common Storage (Nucleus, SQA, CSA) to be accessible to both programs. In the early days of MVS especially, when only 24-bit addressing existed, Common Storage was very constrained.

### What is "Cross Memory"?

MVS Extended Addressability Guide

setting up a cross memory environment

provides details and examples for

Cross memory is the mechanism to provide SYNCHRONOUS communication between address spaces for the purpose of sharing function or data.

- A program can acquire access to other address spaces' storage or code

- The program controls the cross memory environment

- Hardware/Architecture.....

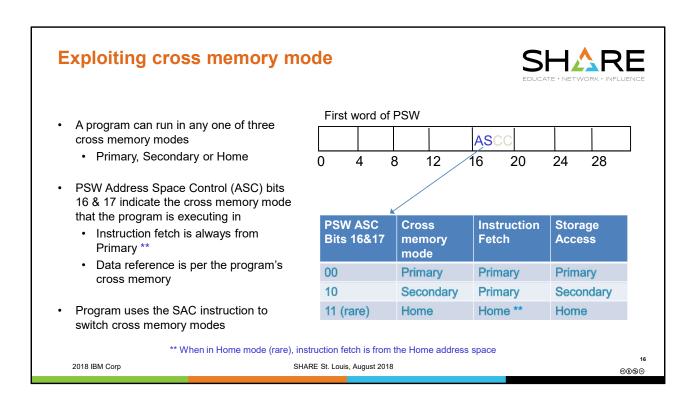

- Bits in the PSW ASC mode

- Control registers

- Special instructions PC, PR, PT, SSAR, SAC, MVCP, MVCS, etc

- Architected structures created by z/OS, referenced by hardware

- PC linkage tables, linkage stacks, ASTEs, authorization tables, etc

2018 IBM Corp SHARE St. Louis, August 2018 @0%9

Providing a SYNCHRONOUS mechanism to communicate between address spaces improves performance by avoiding the schedule/wait/schedule/post asynchronous communications, and allows direct access to private storage, eliminating the need to keep shared data in common storage. Data is isolated to only the programs that have access, and the common storage constraint is relieved.

The <u>MVS Extended Addressability Guide</u> is an excellent reference for discussion and examples of cross memory concepts.

Items highlighted in blue will be discussed later in the presentation.

### **Cross memory concepts**

#### HOME

- the dispatched address space i.e. where a program starts off life, where its associated TCB resides

#### PRIMARY

the address space where a program is presently executing i.e. where instructions are being fetched \*

### SECONDARY

- the address space that was primary before the last PC (program call) instruction

ALL programs begin life with HOME=PRIMARY=SECONDARY

\*except in PSW ASC mode HOME

2018 IBM Corp

SHARE St. Louis, August 2018

The whole purpose of cross memory addressability is to extend a program's "reach". A program running in an environment where Home, Primary, and Secondary are all different has ready access to the code and data in 3 different address spaces. An example of this will be provided shortly.

To be discussed later, access registers offer an alternate and more powerful way of extending a program's addressability. Access registers can be used to gain access to data spaces, as well as to easily address data in other address spaces.

# How do home, primary, and secondary change?

- HOME \*never\* changes!!

- Instructions that update PRIMARY & SECONDARY

- PC (program call)

- PR (program return)

- PT (program transfer)

- The SSAR instruction updates SECONDARY

2018 IBM Corp

SHARE St. Louis, August 2018

**9**⊕⊛⊜

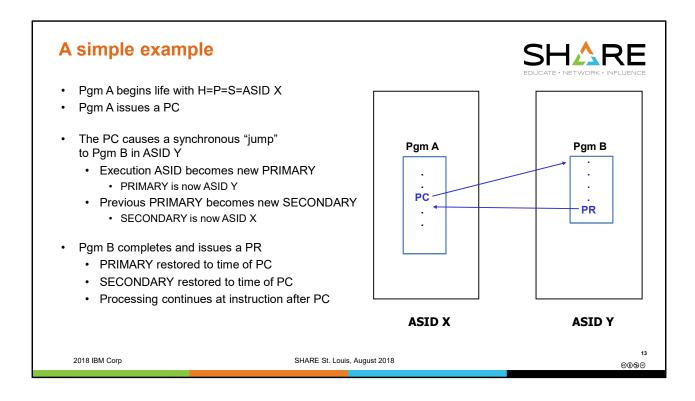

#### Reminder:

- Home is where a program starts life.

- Primary is where a program is presently executing.

- Secondary is typically where a program was executing prior to its last PC.

- SSAR can be used to set secondary to something else.

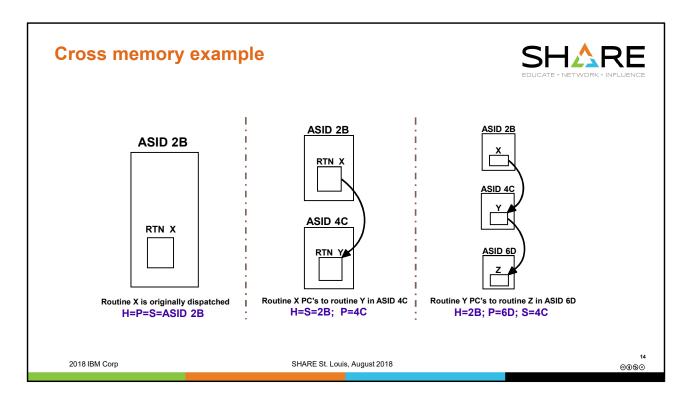

A job X begins in ASID 2B. Home, primary, and second address spaces are all the same at this point.

Routine X PCs to Routine Y in ASID 4C. ASID 4C is now the new PRIMARY. ASID 2B, the previous PRIMARY, is now the new SECONDARY. HOME is ASID 2B, the dispatched address space, and will not change.

Routine Y PCs to ROUTINE Z in ASID 6D. ASID 6D becomes the new PRIMARY, ASID 4C becomes the new SECONDARY, and ASID 2B remains HOME.

At this point, we have ready addressability to 3 different address spaces.

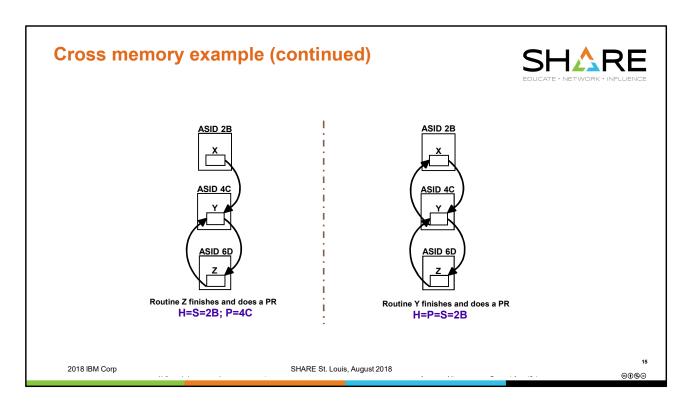

When Routine Z finishes, it returns to Y in ASID 4C via PR. ASID 4C becomes the new PRIMARY, ASID 2B becomes the new SECONDARY (as it was before Y PC'd to Z), and ASID 2B is still HOME.

Routine Y finishes, and returns to X via PR. PRIMARY is again ASID 2B, SECONDARY is again ASID 2B. HOME is, and always has been, ASID 2B. At this point, we are back to H=P=S=2B.

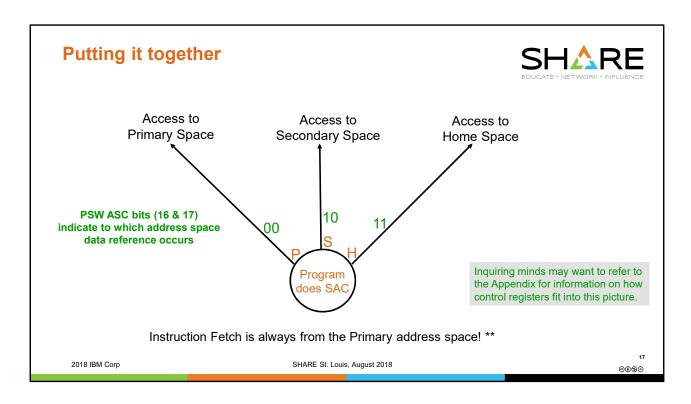

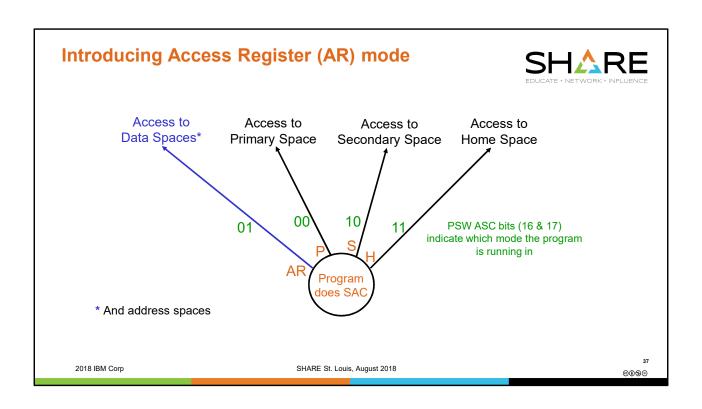

An executing program controls the cross memory mode that it wants to execute in. Typically it will run in primary mode where it has ready access to the primary address space's data. However it can easily SAC to secondary to gain access to the data in the secondary address space instead, or it can SAC to home to gain access to the data in the home address space. When a SAC instruction is executed, it updates the PSW ASC bits (16 and 17) in the PSW. This is what tells the hardware whether to access storage in the primary, secondary or home address space when machine instructions are executed.

The PSW ASC mode does not influence instruction fetch (except in the unusual case of running in home mode). Except in the case of home mode, instruction fetch always is from the primary address space.

The SAC instruction acts like a dial that a program can turn back and forth to control which address space's storage (primary, secondary, or home) it wants to access.

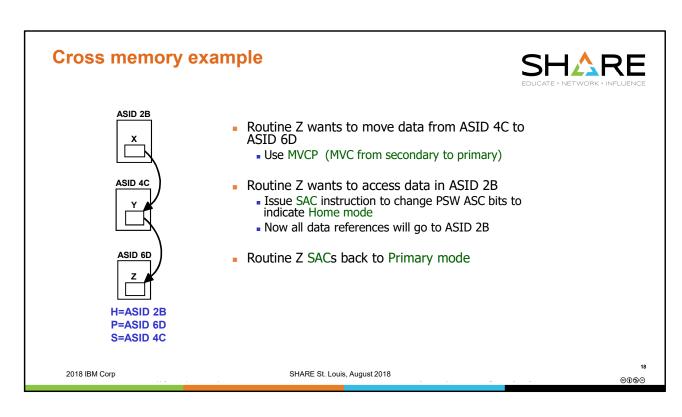

When Routine Z is PC'd to, we assume Routine Z has not yet issued SAC to change PSW ASC mode, so assume PSW ASC mode is PRIMARY, which means that all data references will be made to current PRIMARY, 6D. If Z wants to move data from ASID 4C (SECONDARY) to ASID 6D (PRIMARY), it can use MVCP.

To access data in ASID 2B, Z can issue SAC to HOME. Now all data references (LOAD, STORE, MVC, etc.) will occur in ASID 2B. Remember that when in HOME mode, instructions are also fetched from the HOME address space. This means that Routine Z had better live in common (global) storage if its instructions are to be successfully accessed both from the HOME space and from the PRIMARY space! In our diagram, a PC to routine Z results in a space switch to PRIMARY=ASID 6D. Note that it is perfectly okay for a space-switching PC routine to live in global storage.

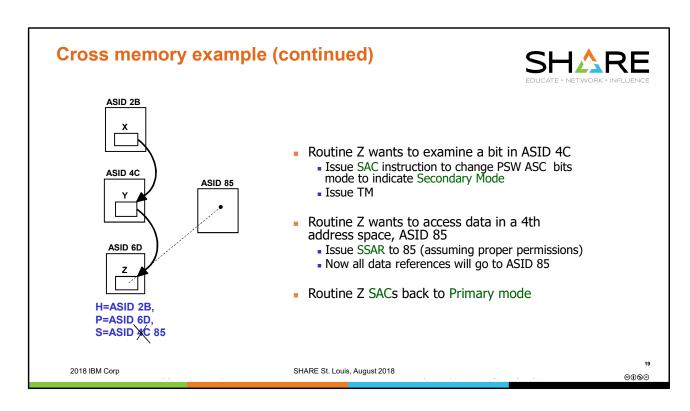

We are using the same example as before, except now Routine Z wants to access data in a 4<sup>th</sup> address space, not one that it PC'd through.

Assuming the authority has been granted, Z can SSAR to ASID 85 to designate ASID 85 as the new SECONDARY. Then a SAC to SECONDARY allows all data references to occur in ASID 85 until Z SACs back to PRIMARY.

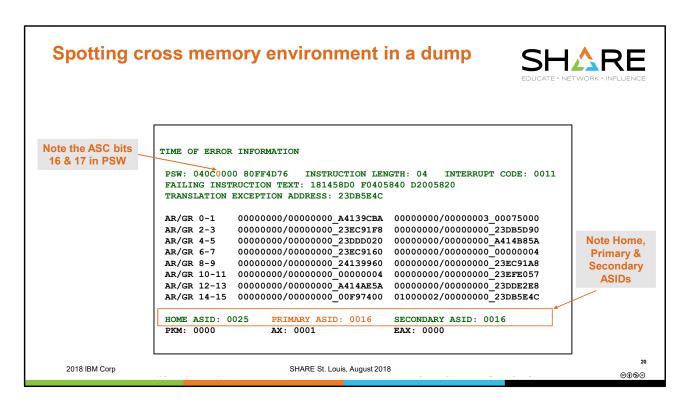

The highlighted zero in the PSW shows ASC mode bits 16-17 are both zero – Primary mode. The dispatched address space is ASID x'25', but execution is in PRIMARY ASID x'16'. Data reference is also in ASID x'16'.

### **PC** routines

- PC instruction

- Only operand is PC number

- PC number identifies target routine (aka PC routine)

- Every address space has a unique PC table

- Each entry maps a PC number to a PC routine address and ASID

- A space switching PC "jumps" to a routine in another address space

- A non-space switching PC "jumps" to a routine with the same address space

- Some entries common across all address spaces, e.g. STORAGE OBTAIN = 30B

- Types of PC routines

- Stacking Exploits linkage stack hardware to automatically save/restore status ③

- Basic Old, unfriendly, less efficient; must explicitly save/restore status ⊗

2018 IBM Corp SHARE St. Louis, August 2018 @096

The PC number uniquely identifies a target routine which may or may not reside in a different address space. The PC number is actually comprised of 2 concatenated indices that hardware uses to index into tables, ultimately mapping a PC number to a target routine.

Some PC numbers are system-defined. These belong to system services invoked via the PC instruction.

For more information on system-defined PCs, see <u>MVS Diagnosis</u>: <u>Reference</u>, Chapter 5: Program Call (PC) Services in System Function Table.

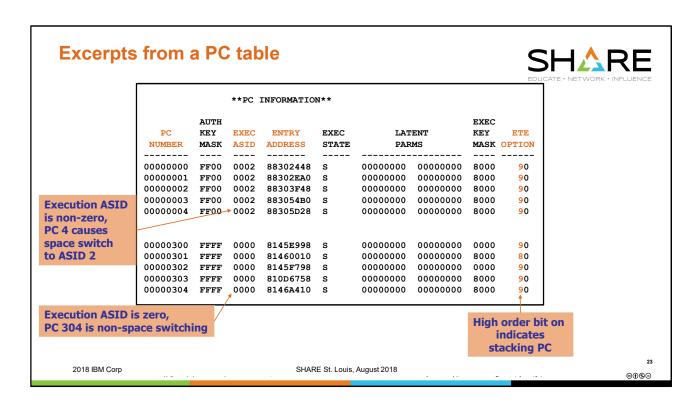

## Reading a PC table

- To see what PC numbers are defined for a particular address space:

- IP SUMMARY FORMAT ASID(X'yy') Use primary ASID

- FIND 'PC INFORMATION' to locate the PC table

- Each entry in the PC table includes:

- PC number

- PC routine address (receives control when PC issued)

- ASID that the PC routine executes in

- Indication of stacking vs basic

- Indication of space switching vs non-space switching

- Information related to authorization and recovery

The PC Information table is located near the top of IP SUMMARY FORMAT, just under the address space-related control blocks and before the TCBs. Note that applications can create their own unique, address-space-specific PC's, so it is very important to review IP SUMMARY FORMAT for the PRIMARY address space at the time the PC was issued to obtain accurate information about the target PC routine.

Use IPCS WHERE on the Entry Address qualified with the EXEC ASID (example: IP W 08302448 ASID(2) ), or browse storage in the EXEC ASID to identify the routine that will receive control for a given PC.

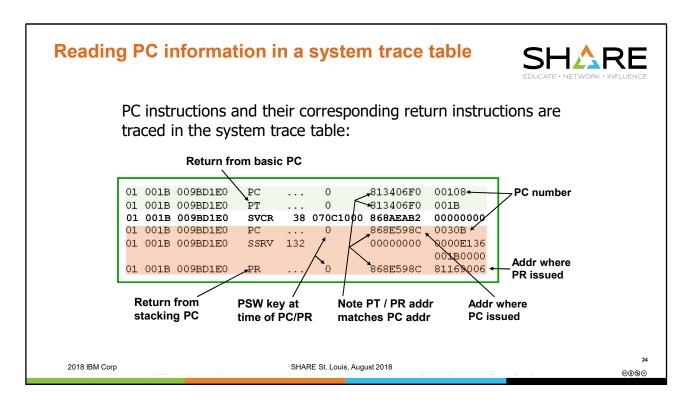

A PC entry will have the same PSW address as its corresponding PT or PR instruction.

PC / PR or PC / PT entries can be nested. When looking at these entries in a system trace table, match them up using the PSW address, similar to matching up SVC / SVCR entries in a system trace table or DO / END statements in a computer program.

You cannot tell if a PC instruction is basic (and so will be matched with a PT) or stacking (and so will be matched with a PR) directly from the system trace table. You could take the PC number and look it up in the SUMM FORMAT PC Information Table, but its generally easier to just match up PSW addresses in order to locate the PT / PR.

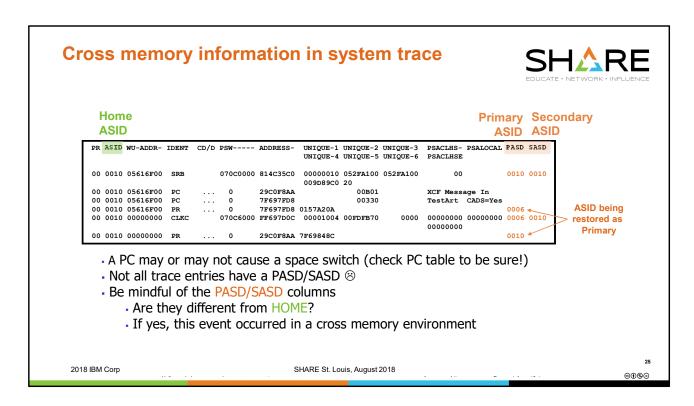

When analyzing the System Trace Table, be alert to possibility of a cross memory environment. On the left is the dispatched address space (HOME), but on the right (you may need to adjust your screen or shift right) you will see 2 columns, PASD and SASD (PRIMARY ASID and SECONDARY ASID). If these are different than HOME, that trace entry represents an event that occurred in a cross memory environment. It is good practice to pay close attention to these two columns.

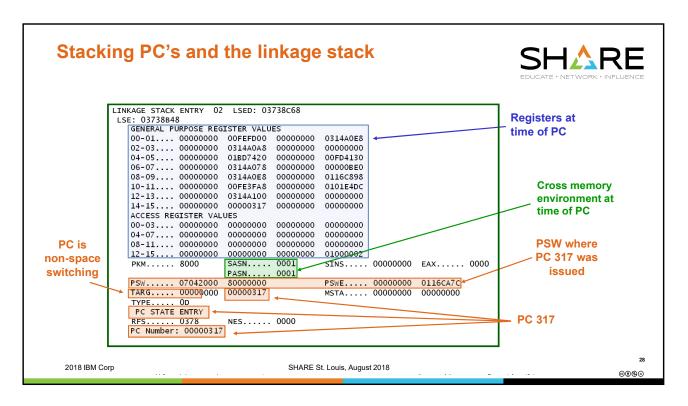

## Stacking PC's and the linkage stack

### A linkage stack is an architected stack of save areas

- Every unit of work (TCB / SRB) has a linkage stack

- When a stacking PC is issued, the unit of work's status is automatically saved as the top entry on its linkage stack (LSE)

- PSW

- Registers

- Cross memory environment

- LSE also contains the PC number and execution ASID

- A PR restores status from that entry and removes it from the stack

- BAKR instruction also exploits the linkage stack

- Typically used on entry to a module in place of standard save area linkage

- Status restored on exit from module via a PR

- BAKR's and their corresponding PR's are not traced

2018 IBM Corp

SHARE St. Louis, August 2018

**⊕⊕**⊕€

The exploitation of linkage stacks by stacking PCs provides an easy and efficient way to save program status as program A PC's to program B. For this reason a BAKR instruction was also added with the linkage stack architecture so that code that is not a PC routine can exploit the convenience of the linkage stack. A BAKR (branch and stack register) instruction with RO specified as the target of the branch (meaning don't branch) can be used on program entry to save the caller's status on the linkage stack. This technique is much simpler than using standard save area logic. Similar to a PC instruction, a PR "undoes" a BAKR instruction by restoring status from the linkage stack.

## Reading a TCB's linkage stack

- Locating a TCB's linkage stack

- Issue: IP SUMMARY FORMAT ASID(x'yy')

- FIND 'TCB: 00xxxxxx' where xxxxxx is the address of your target TCB

- FIND LINKAGE to get to the linkage stack data

- Linkage stack format

- Stack could contain many entries or none

- Entries are formatted oldest to newest

- Only "in use" entries are formatted

2018 IBM Corp

SHARE St. Louis, August 2018

⊕⊛∋

There is nothing of interest in the linkage stack header and trailer entries. They are only mentioned here because they may be formatted out in SUMM FORMAT, albeit inconspicuously. The interesting linkage stack entries are the "state" entries which are where the save area information is stored.

Only "in use" linkage stack entries are formatted. Once an entry is popped off the linkage stack (i.e. once you see a PR for it, for example, in the system trace table), then you will no longer see that entry formatted in SUMM FORMAT. The data remains residually in the linkage stack entry until it is reinitialized as a result of a new stacking PC or BAKR.

This is a linkage stack entry created as a result of code in ASID X'1' issuing a PC 317.

Note that the Primary and Secondary Address Space Numbers (PASN and SASN) are from the time the PC was issued, not after it was executed. The first 2 bytes of the TARG indicate whether the PC is space-switching. If 0 (as in this example), it is non-space switching. If non-zero, then the PC routine will get control in the designated address space.

Note: the PASN field actually appears to the right of the EAX field in SUMMARY FORMAT. In the interest of readability, a field called PINS which was to the right of PASN has been omitted from this example.

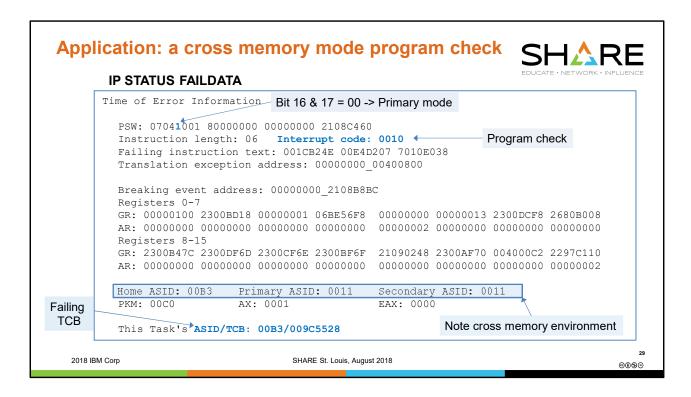

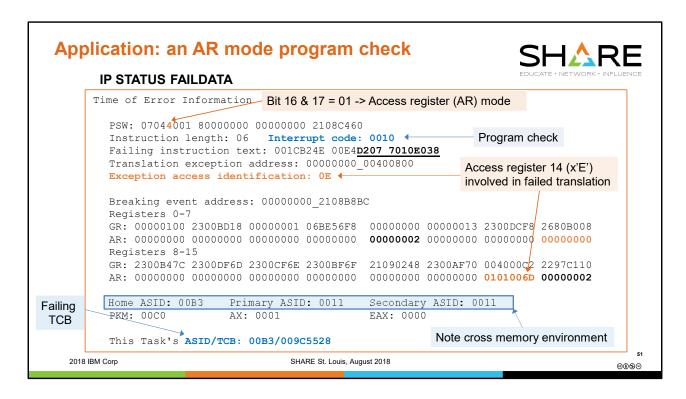

This is Time of Error Information from a dump of a program check, an ABENDOC4 PIC10.

Note the PSW ASC bits. These are PSW bits 16 and 17, that is, the first 2 bits of the  $5^{th}$  nibble. This nibble contains a X'1' = B'0001'. The first 2 bits are B'00' which indicates Primary Mode. This means that both the instruction fetch and the data references are to the primary address space.

Underneath the registers at time of error we see the cross memory environment at time of error. The Home address space is ASID X'B3'. The primary and secondary ASIDs are both ASID X'11'. Remember that home is where the unit of work started off life, its original ASID, its job. Primary is the address space in which the unit of work is currently executing. The error occurred in primary mode, so it occurred when trying to access storage in the primary address space.

It is also handy to note the address of the failing TCB. The TCB lives in the home address space.

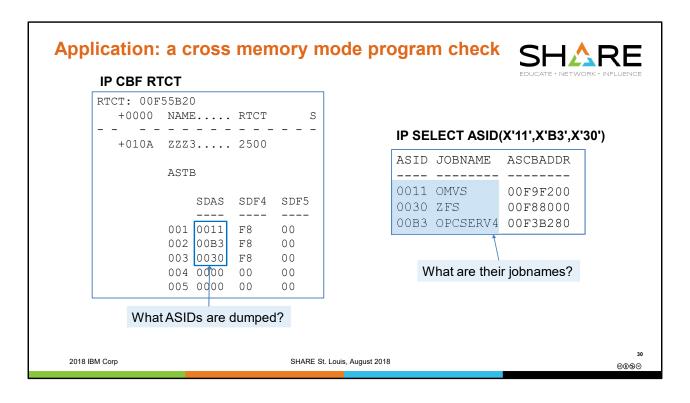

The 'IP CBF RTCT' command identifies the ASIDs included in an SVC dump. The 'IP SELECT' command allows us to associate a JOBNAME with each ASID. 'IP SELECT ALL' can be used to show all active ASIDs and their associated JOBNAMEs.

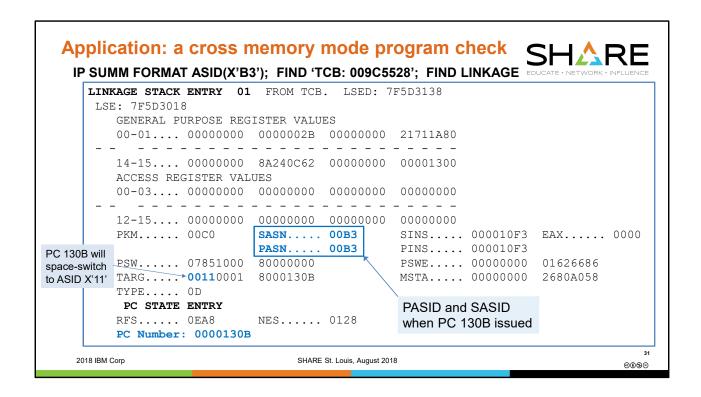

The first linkage stack entry (LSE) under the error TCB shows a PC 130B being issued. At the time of the PC 130B being issued, HASID=PASID=SASID=X'B3'. As a result of the PC 130B being issued, a space switch occurs into ASID X'11'. Following the issuance of the PC, HASID=B3, PASID=11, and SASID=B3.

To determine the address of the PC routine which receives control in ASID 11 as a result of the PC 130B, consult the PC Information Table near the top of the SUMMARY FORMAT report.

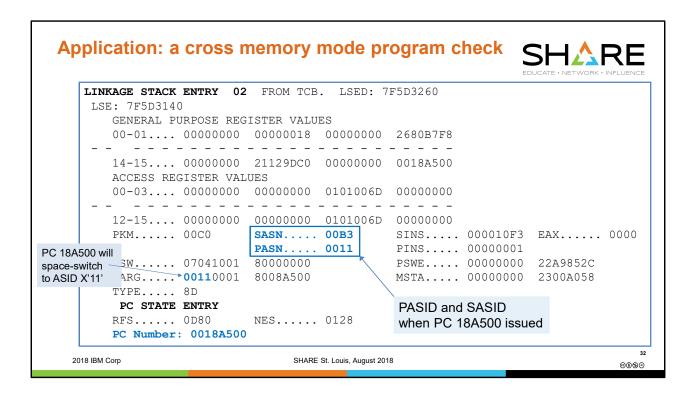

The second linkage stack entry under the error TCB shows a PC 18A500 being issued. At the time of the PC 18A500 being issued, HASID=B3, PASID=11, and SASID=X'B3'. As a result of the PC 18A500 being issued, a space switch occurs into ASID X'11'. Since the unit of work was already running with PASID=11, this does not cause a change of the primary address space; however it does cause the SASID to be updated to become ASID 11.

Following the issuance of the PC 18A500, HASID=B3, PASID=11, and SASID=11.

In last line of this LSE, we see for the first time a "big" PC number, that is, one that is greater than X'0007FFFF'. This represents an architectural change introduced when the ASN-and-LX-Reuse facility was implemented. The X'00080000' bit in this word represents a flag which is part of the <u>uncompressed PC</u> number. You can find the uncompressed PC number in the IPCS SUMMARY FORMAT PC Information Table and in system trace table PC entries, in addition to on this "PC Number:" line (if present) of the LSE. However the second word of the LSE's TARG field will contain the <u>compressed PC</u> number. To derive the compressed PC number from the uncompressed PC number, turn off the flag bit, and shift all bits to the left of it right by 1 bit position. In the example above, 0018A500 becomes 0010A500 when the flag bit is turned off, then shifting X'001' right by 1 bit results in 0008A500. As another example, uncompressed PC number 00490113 becomes 00410113 when the flag bit is turned off, then shifting X'004' right by 1 bit results in 00210113.

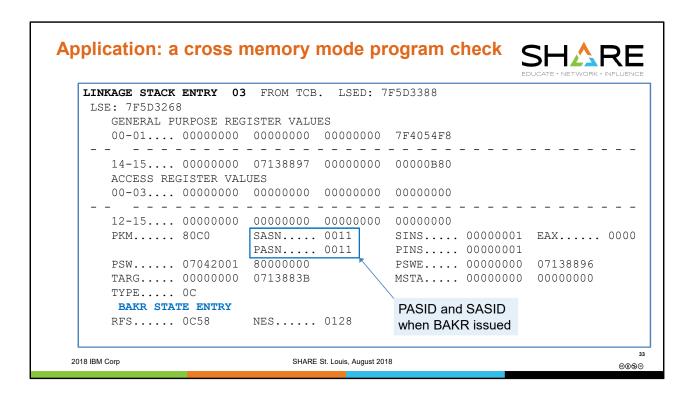

The third linkage stack entry under the error TCB was created as a result of a BAKR instruction. This instruction is often issued on entry to a routine for the express purpose of taking advantage of the linkage stack as a status save area. At the time of the BAKR being issued, HASID=B3, PASID=11, and SASID=11. A BAKR instruction does not affect Home, Primary, and Secondary.

The TARG field indicates the address where the BAKR was issued.

### **Application: a cross memory mode program check** IP SYSTRACE ASID(X'B3') TCB(X'9C5528') TI(LO) ASID WU-Addr- Ident CD/D PSW----- Address- Unique-1 Unique-2 Unique-3 PSACLHS- PSALOCAL PASD SASD PR ASID WU-Addr Ident CD/D PSW---- Address Unique-1 Unique-2 Unique-3 PSACL 0000 00B3 009C5528 PC ... 8 01626609 00\_20DD601C 0000 00B3 009C5528 PR ... 0 01626687 0130B read/ 0000 00B3 009C5528 PC ... 0 3 22A9852C 0018A500 0000 00B3 009C5528 PC ... 0 0\_20C3C6FC 00B33 XCF 0000 00B3 009C5528 PC ... 0 0\_7F776B7A 00330 TestA 0000 00B3 009C5528 PR ... 0 0\_7F776B7A 016ED824 0000 00B3 009C5528 PR ... 0 00\_20C3C6FC 7F7734EE 0000 00B3 009C5528 PR ... 0 00\_20C313BO 0030D Wait 0000 00B3 009C5528 PR <td read/write TestArt CADS=Yes 0006 00000000 0009 00B3 009C5528 PR 00\_20C313B0 00 00FEC5E8 0009 00B3 009C5528 PGM 010 00000000\_2108C460 00060010 00000000 00000000 00000000 0011 0011 07044401 80000000 00400801 00000000 0009 00B3 009C5528 \*RCVY PROG 00000000 2018 IBM Corp SHARE St. Louis, August 2018 @**(1)** (8) (2)

Note that we've formatted the system trace table using the ASID and the TCB filter so that we can focus just on activity under our error TCB. We can see the PC 130B and the PC 18A500, which we saw on our linkage stack, in our system trace table. They have no matching PR because processing as still going on within this PC routine environment at the time that the program check occurred.

A few PC's have been issued after the PC 18A500, which was the last seen on the linkage stack. We don't see these PC's on the linkage stack because the PC routines have completed and issued the PR, which removes the entry from the linkage stack.

Note that some trace table entries trace the PASID and/or SASID at the time the event occurred.

Since linkage stack entries contain PSW and register information, they are very valuable for debugging!

# **EXTENDED ADDRESSABILITY**

2018 IBM Corp SHARE St. Louis, August 2018

@**(**)

# **Getting greedy: Data spaces and access registers**

- Problem (pre-z/Architecture): Address spaces were limited to 2Gig in size

- Needed more private storage

- Needed more common storage

- Solution (pre-z/Architecture): Data spaces!

- Data-only spaces up to 2Gig in size

- Can be used for private or common storage needs

- Address spaces can own multiple data spaces

- Addressable through "access register" paired with corresponding general purpose register

- GPR identifies virtual address to access

- AR identifies the data space that the virtual address is in

- Only accessible by programs running in Access Register (AR) mode

2018 IBM Corp

SHARE St. Louis, August 2018

@**()** (\$(=)

In the world prior to z/Architecture (pre-Year2000), address spaces were 2Gig in size. Jobs often found themselves needing more storage. The solution was to obtain data spaces to provide additional data repositories beyond the address space's private storage. Data spaces can also be used to hold common storage. Each data space can be up to 2Gig in size, and an address space can have many data spaces.

Access to a data space is accomplished via an access register. We will see that, when running with the PSW ASC bits indicating AR mode, an Access Register is used in conjunction with its corresponding General Purpose Register any time an instruction is executed that has that GPR as a base register. For example, a LOAD off of base register 6 would use AR6 as part of the translation. The GPR would indicate the virtual address to be accessed. The AR would indicate what space that virtual address was in.

yo zos rsm services, i was told to talk to u about getting some storage

You've come to the right place, data spaces are us! Common or private? What size did you have in mind?

pvt, max i can get

Gotcha, 2gig it is, brb

Ok I have your data space ready. Its ID is "xyz". Now you just need to chat with Aly on the xmem service team. Give her this ID and she'll set you up with some buyer protection and give you the key to your new data space.

k ty!

2018 IBM Corp

SHARE St. Louis, August 2018

38

@**()**(\$(=)

# Dramatization via chat: Setting up a data space yo xmem services, was advised to chat with Aly regarding a key to my new data space Hi, this is Aly! Welcome to xmem services. I can get you all set up. What's your data space ID? xyz Great! And as far as who can access your storage, which option would you like: "friends & family" or "personal use only"? whats the dif?? whats the dif??

With "friends & family", anyone executing in your address space can access your data space storage if you share your key with them.

With "personal use only", only code running under your TCB can use your key.

But if you want to be able to access your data space even after you've PC'd into another address space, then the "personal use only" TCB option is the only way to go.

def want all my friends to be able to use this too!

2018 IBM Corp SHARE St. Louis, August 2018

(⊜

@(1)(S)(E)

Ok, "friends & family" it is! One moment please while I get this set up for you.

Ok, I've set up your protection and activated your key. Your key code is 01xx00yy. To use it, just have your program place it in an access register, set up the corresponding general purpose register to point to the address you want to access, and use that register as the base register of an assembler instruction such as a LOAD, STORE, TM, MVC ... any instruction that has a base reg!

Don't forget you must be in AR mode for this to work!

awesome thx much!

2018 IBM Corp SHARE St. Louis, August 2018

**90**9⊝

You're very welcome. Is there anything else I can help you with today?

nope ty, u've been great, working with zos service is always a fantastic experience, u guys rock!

2018 IBM Corp

SHARE St. Louis, August 2018

42 (a)

#### **Access lists**

- An access list is a structure that controls program access to data spaces or address spaces

- Think of an access list as a row of gates to various destinations (data spaces or address spaces) and an ALET is a key to a gate

- Every address space has an access list

- PASN-AL = Primary Address Space Number access list

- Can be used by "Friends & Family", those executing in address space

- Every task and every SRB has an access list

- DU-AL = Dispatchable Unit access list

- Can be used only by code running under the task (TCB) or SRB

2018 IBM Corp SHARE St. Louis, August 2018 @099

Every address space has an access list that can be 500+ entries in size, representing the theoretical ability to set up access to 500+ data spaces/address spaces for programs executing within a specific address space. The address space-related access list is called a PASN Access List.

Every TCB and SRB on the system also has an associated access list. Only programs running under this unit of work can use that access list.

#### The ALET

- Pgm issues DSPSERV to define data space OR ASCRE to define addr space

- Output: A unique ID called a STOKEN is returned

- Pgm issues ALESERV to set up access to data space

- Input: a STOKEN and an indication of which access list to use: PASN-AL or DU-AL

- Output: Indicated access list updated, ALET returned

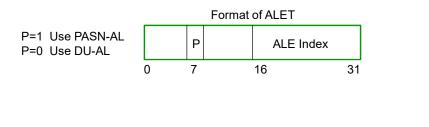

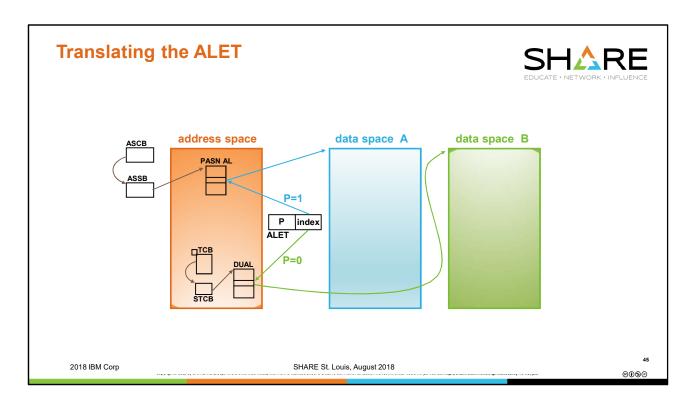

Bit 7 of an ALET is used to determine which access list to use – PASN-AL or DU-AL. The low half of the ALET is the index into the access list.

SHARE St. Louis, August 2018

#### Examples:

2018 IBM Corp

ALET 01000014 - P bit on, use PASN-AL, index is x'0014'

ALET 0000002E – P bit off, use DU-AL, index is x'002E'

Bit 7 of an ALET, the P bit, determines which access list the ALET is associated with.

The low half-word of the ALET is the index into the designated access list.

The same ALET index can reach 2 entirely different dataspaces through the 2 different access lists, determined by bit 7 in the ALET.

A program running in AR mode can use an ALET to address a data space through either the PASN access list or the DUAL access list, depending on the content of the ALET.

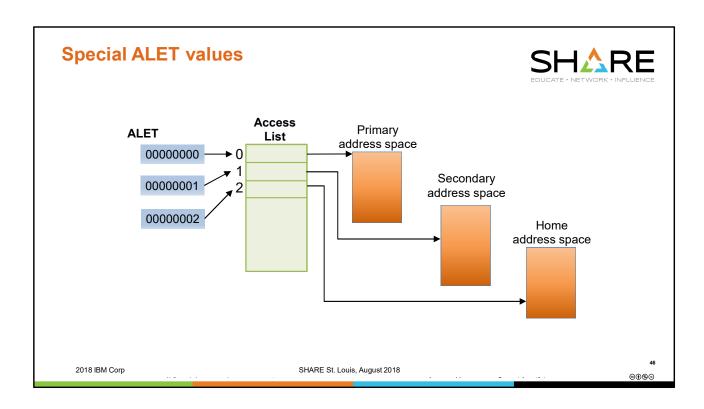

When executing in AR mode (PSW ASC bits '01'), a program can access PRIMARY, SECONDARY, and HOME by loading access registers (ARs) with 00000000, 00000001, or 00000002, respectively. All access lists are initialized so that the first 3 entries (index 0, 1 and 2) will reach these address spaces.

Consider a program running initially with empty (zero) access registers – a good programming practice. The program SACs to AR mode. All data references will occur in the current primary address space (where the program is executing) unless/until specific ARs are loaded with ALETs for addressability to other spaces.

In this example of an ABENDOC4 PIC11 error, the PSW has bits 16-17 = 01 indicating the program is running in AR mode. This means that when a general purpose register indicating a virtual address to be accessed is used as a base register, the corresponding access register will be used to indicate the space (address space or data space) that the virtual address is in. In this case we see that the failing instruction used a base register of 4, so the ALET in AR4 was used as part of the translation. The ALET has the P bit (bit 7) on and so will translate against the PASN access list.

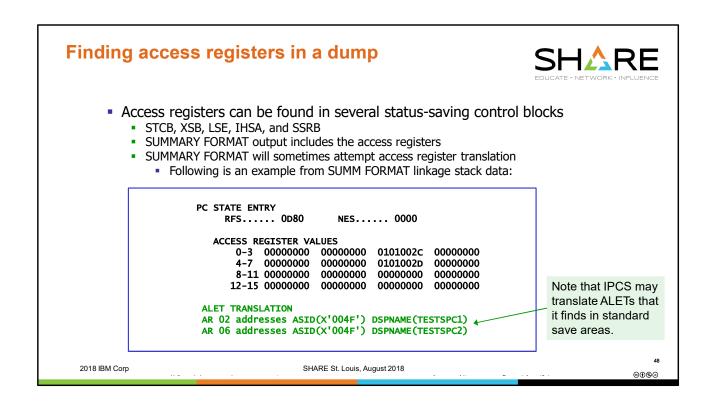

IPCS will attempt to translate ALETs to a data space name in several IPCS reports such as SUMMARY FORMAT.

| Trans    | slating an ALET SHA                                                                                                                                                                                                   | RE                                 |

|----------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------------------------|

|          | Use hidden IPCS option 2.6i :                                                                                                                                                                                         | RK • INFLUENCE                     |

|          | To display information, specify "S option name" or enter S to the left of the option desired. Enter ? to the left of an option to display help regarding the component support.                                       |                                    |

|          | S Name Exec Abstract  S ALET2DSP IAXAR2D DataSpace Name associated with input AR/ALET  CMD2FILE BLSXC2FI Writes output from an input IPCS cmd to output dataset  CPUINFO IEAVCPUI displays high level CPU information |                                    |

|          | SELECT OPTION ===>                                                                                                                                                                                                    | 7                                  |

|          | ALET Value : ALET value should start in 01.                                                                                                                                                                           | wise see<br>ECK in the<br>Commands |

|          | ALET value should be 8-digit hexadecimal (eg. 01xxxxxx). ASID Value should be 4-digit hexadecimal.                                                                                                                    |                                    |

| 2018 IBM | Corp SHARE St. Louis, August 2018                                                                                                                                                                                     | <b>49</b><br>©(†)(§)(≘)            |

An undocumented (but safe!) REXX exec called ALET2DSP will help you easily translate an ALET for the PASN access list to its corresponding space. However this REXX exec does not handle ALETs for a DUAL access list. For DUAL ALETs, you will need to refer to the IP ARCHECK command. When passing a DUAL ALET to the ARCHECK command, you need to supply the ALET, the home ASID, and the address of the DUAL as pointed to by STCBALOV. Here is an example:

#### ARCHECK ALET(X'0001002B') ADDR(7F6C1600) ASID(X'3C') STR(ACCESSLIST)

ARCHECK can also be used to translate PASN AL ALETs. However in that case you will need to provide the address of the PASN AL as pointed to by ASSBPALV, along with the primary ASID.

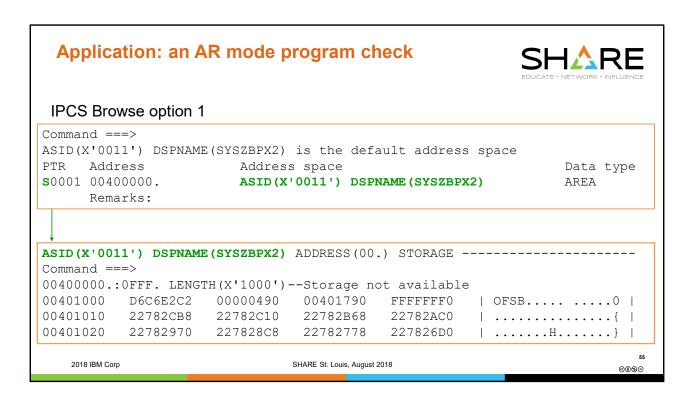

### Displaying data space storage

- To display data space storage....

- Issue: IPCS LIST xxxxxxxx LEN(X'ww') ASID(X'yy') DSPNAME(zzzzzzzz)

- xxxxxxxx is the virtual storage address to be viewed

- ww is the length of storage to be viewed

- zzzzzzzz is the name of the data space

- yy is the ASID of the address space with which the data space is associated

**OR**

Use IPCS option 1 Browse:

PTR Address Address space

00001 0000B000. ASID(X'001D') DSPNAME(MYSPACE)

2018 IBM Corp SHARE St. Louis, August 2018

9⊜

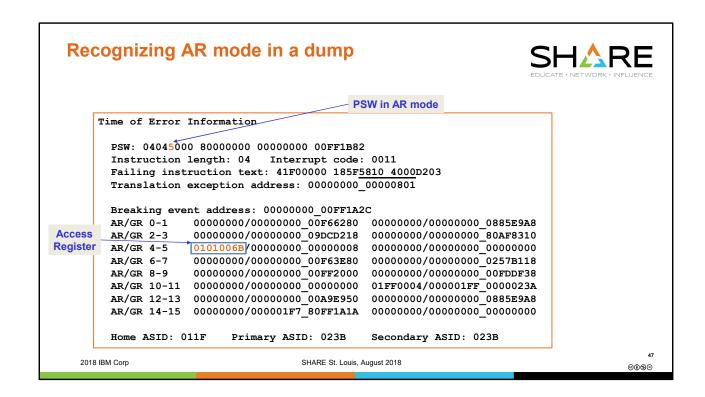

This is Time of Error Information from a dump of a program check, an ABENDOC4 PIC10.

Note the PSW ASC bits. These are PSW bits 16 and 17, that is, the first 2 bits of the  $5^{th}$  nibble. This nibble contains a X'4' = B'0100'. The first 2 bits are B'01' which indicates Access Register Mode. This means that the instruction fetch is from primary and the data references are determined by the ALET in the access register(s) corresponding to the instruction's base register(s). Access register 14 is identified as being involved in the translation failure.

Note that some access registers contain 00000002. An ALET of 00000002 indicates the home address space. If the access register corresponding to an instruction's base register contains an ALET of 00000002, then the storage access will be to the address indicated by the general purpose base register in the home address space.

Many access registers contain 00000000, which indicates the primary address space.

Beneath the registers we see the cross memory environment identified. Home ASID=B3. Primary ASID=11. So use of an ALET of 00000002 accesses ASID B3. Use of an ALET of 00000000 accesses ASID 11. The failing instruction is attempting to move data from the space indicated by the ALET of 0101006D to the primary address space, ASID 11.

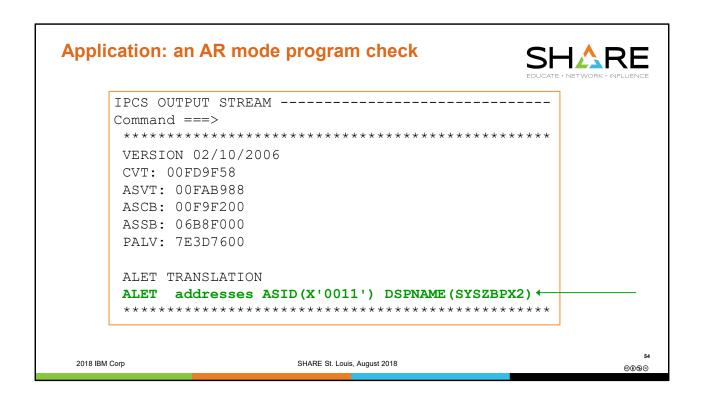

#### **Application: an AR mode program check** To translate a PASN-ALALET, go to hidden IPCS option 2.6i and select ALET2DSP ----- IPCS MVS LEVEL 2 TOOLKIT -----OPTION ===> SCROLL ===> CSR Level 2 toolkit functions are intended to be used as directed by service To display information, specify "S option name" or enter S to the left of the option desired. Enter ? to the left of an option to display help regarding the component support. S Name Exec Abstract S ALET2DSP IAXAR2D DataSpace Name associated with input AR/ALET CMD2FILE BLSXC2FI Writes output from an input IPCS cmd to output dataset CPUINFO IEAVCPUI displays high level CPU information Select 2018 IBM Corp SHARE St. Louis, August 2018 @**(1)**

If the P-bit (bit 7 counting from 0) of the ALET is on, then the ALET is a primary ALET and maps to the PASN access list. In this case, exec ALET2DSP can be used to translate the ALET to a space. Choose IPCS option 2.6i and Select ALET2DSP. You will be prompted to enter the ALET and the primary ASID.

Note that IPCS option 2.6i contains many "as-is" rexx execs. These are "lightly" supported, meaning that if a defect is found in the exec, it will not be APAR'd, but it might be addressed in the next release. See August 2017 SHARE presentation "Mining z/OS Debugging Nuggets" for additional information about execs available under option 2.6i:

http://events.share.org/Summer2017/Public/SessionDetails.aspx?FromPage=Speakers.aspx &SessionID=3547&nav=true&Role=U%27

To translate a DU-AL ALET, use the ARCHECK command.

# Application: an AR mode program check

```

SELECT OPTION ===>

Enter the following inputs.

ALET Value: 0101006D - ALET value should start in 01.

ASID Value: 0011

ALET value should be 8-digit hexadecimal (eg. 01xxxxxx).

ASID Value should be 4-digit hexadecimal.

IAXAR2D exec will show the output of the ARCHECK command by taking two input values, the ASID and ALET value, and provide the corresponding Dataspace name associated with that ALET value.

```

2018 IBM Corp

SHARE St. Louis, August 2018

• ••••

The output of the ALET2DSP exec shows that ALET 0101006D mapped against the PASN AL for ASID X'11' translates to DSPNAME SYSZBPX2, owned by ASID X'11'.

To browse storage in a data space, specify the data space name and the owning ASID. You can scroll through a data space and use indirection symbols to navigate a data space, just as you can with an address space.

You can also LIST data space storage in a similar fashion, for example:

IP LIST 00400000 ASID(X'11') DSPNAME(SYSZBPX2) LEN(X'10000')

### Application: an AR mode program check

56

2018 IBM Corp

SHARE St. Louis, August 2018

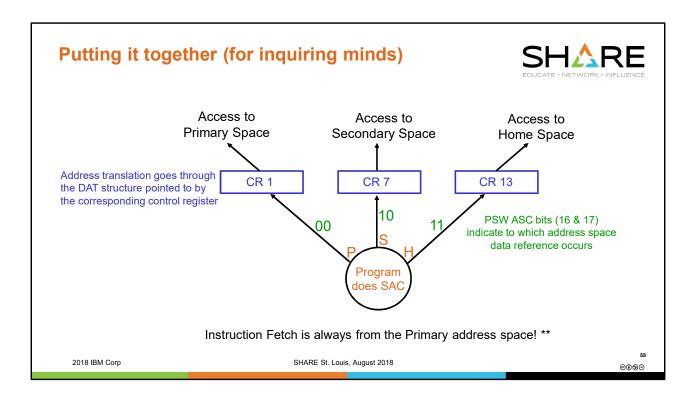

For those who really like to know the in's and out's of what is going on behind the scenes, here is the bigger picture. The operating system has 3 control registers, CR1, CR7, and CR13, which are set up to point to the DAT structures (the dynamic address translation structure -- virtual-to-real address translation tables managed by RSM and read by hardware) for the primary, secondary, and home address spaces respectively. When an instruction which changes the primary or secondary address space is executed (for example, PC, PR, or SSAR), under the covers the control registers are updated accordingly. When an instruction which accesses storage, such as a LOAD or a STORE or a MVC is executed, the PSW ASC mode bit setting tells hardware which control register it should use for translation, i.e. which address space's translation tables should be used for that instruction's storage access.

To summarize, CR1 and CR7 and CR13 define WHAT are the primary, secondary, and home address spaces respectively, while the PSW ASC bit setting indicates WHICH of these 3 address spaces will be used for the executed instruction's address translation.

# Including data spaces in a dump

- SLIP or DUMP Command

- DSPNAME=

- ex: DUMP COMM=JES2DUMP JOBNAME=JES2,DSPNAME=('JES2AUX'.\*'),etc

- ex: SLIP SET,COMP=0C4,JOBNAME=SAPIAPP, JOBLIST=(JES2),DSPNAME=(2B.JES2SAPI),END

- SDUMPX coded macro

- DSPLIST,LISTD,SUMLSTL

- Standalone dumps

- AMDSADMP macro to generate SADUMP program

- Keywords: dataspaces of asid(x) or dataspaces

2018 IBM Corp

SHARE St. Louis, August 2018

©**⊕**®⊕

Various keywords designate data space names to include data space storage in dumps. Refer to <u>System Commands</u>, <u>Authorized Assembler Services Reference</u>, and <u>MVS</u> <u>Diagnosis: Tools and Service Aids</u> for more details.

#### Identifying whether data spaces dumped SHARE IPCS INVENTORY -----Command ===> AC Dump Source Status LZ DSNAME('ONTOP.GS999.P55555.C555.DUMP0F8') . . . . . . . . . . . OPEN Title=COMPON=IOS,COMPID=SC1C3,ISSUER=IOSVIRBA,IRBAFRR Psym=RIDS/NUCLEUS#L RIDS/IOSVIRBA PIDS/5752SC1C3 AB/S00C4 RIDS/IOSVIRBA#R DSNAME('ONTOP.GS999.P35418.C616.XXXXXX.DUMP') . . . Title=CICS DUMP: SYSTEM=ABCDEF CODE=FC0001 ID=1/0007 No symptoms \*\*\*\*\*\*\*\*\* END OF IPCS INVENTORY LZ = list zone 2018 IBM Corp SHARE St. Louis, August 2018

LZ (list zone) is a line command on the IPCS inventory panel that will display a comprehensive report of what the dump contains, including a dumped storage summary showing data spaces and storage ranges dumped.

LD (list dumped) is a subset of this report showing the dumped storage summary, including data spaces.

# Identifying whether data spaces dumped (continued)

#### LIST ZONE REPORT

Report shows ranges dumped for each data space.

2018 IBM Corp

@**()** (\$(=)

Use 'FIND DSPNAME' and repeat FIND to step through all the data spaces dumped, or use 'FIND JES2SAPI' (or other dspname) to search for a specific data space in the body of the report.

SHARE St. Louis, August 2018

# Identifying data spaces owned by ASID

@**()**(\$(=)

- IPCS RSMDATA DSPACE ALL displays all data spaces in the system

- IPCS RSMDATA DSPACE ASID(X'yy') displays data spaces owned by ASID yy

JOBNAME ASID DSP NAME OWNG TCB CUR B MAX B K T S R F TOT R

CONSOLE 000B IEAM02F2 007FD230 00100 00100 0 B A E N 00008

CONSOLE 000B IEEMCS01 00 FD230 80000 80000 0 B S E Y 00024

See the RSMDATA chapter of <u>MVS Diagnosis: Reference</u> for an explanation of this report.

2018 IBM Corp SHARE St. Louis, August 2018

62