SC09-3026-00

# IBM27-82660

## PowerPC to PCI Bridge and Memory Controller User's Manual

© Copyright International Business Machines Corporation 1996

Printed in the United States of America 1996 All rights reserved

Note to US Government Users—Documentation related to restricted rights—Use, duplication, or disclosure is subject to restrictions set forth in GSA ADP Schedule Contract with IBM Corp.

IBM and the IBM logo are registered trademarks of the IBM Corporation. The following terms are trademarks or registered trademarks of the IBM Corporation: IBM Microelectronics, PowerPC, PowerPC 601, PowerPC 603, PowerPC 604, PowerPC Architecture, MicroChannel, and Risc-Watch. All other product and company names are trademarks or registered trademarks of their respective holders.

This document is subject to change by IBM without notice. IBM assumes no responsibility or liability for any use of the information contained herein. Nothing in this document shall operate as an express or implied license or indemnity under the intellectual property rights of IBM or third parties. The products described in this document are not intended for use in implantation or other direct life support applications where malfunction may result in direct physical harm or injury to persons. NO WARRANTIES OF ANY KIND, INCLUDING BUT NOT LIMITED TO, THE IMPLIED WARRANTIES OF MERCHANTABILITY OR FITNESS FOR A PARTICULAR PURPOSE, ARE OFFERED IN THIS DOCUMENT.

- Overview 1

- Pin Descriptions 2

- CPU Bus 3

- PCI Bus 4

- DRAM 5

- L2 Cache 6

- ROM 7

- Exceptions: Resets, Interrupts, Errors, and Test 8

- Endian Mode 9

- Bridge Control Registers 10

- Timing A

- Electrical and Mechanical

- Pin Lists C

## The IBM27-82660 PowerPC™ to PCI Bridge

## Memory, L2, ROM, and System Controller

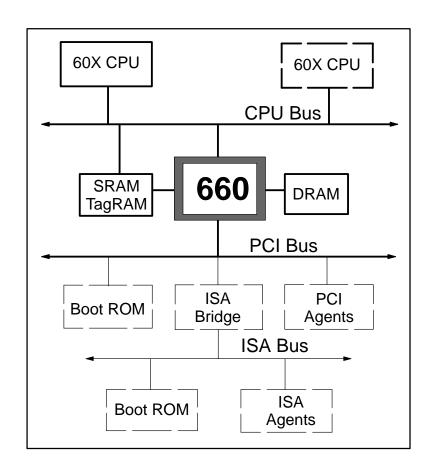

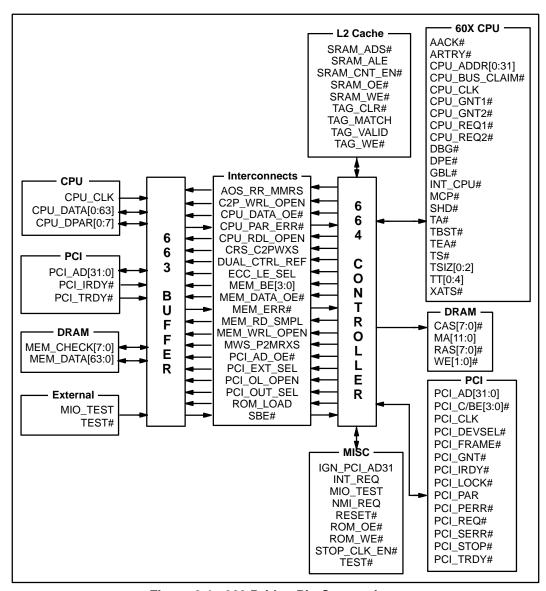

IBM 660 Bridge Chip Set in a Typical System Configuration

#### Minimum Cycle Times For Pipelined CPU to Memory Transfers at 66 MHz

| Responding Device           | Read     | Write    |

|-----------------------------|----------|----------|

| L2 (9ns Synchronous SRAM)   | -2-1-1-1 | Snarf    |

| L2 (15ns Asynchronous SRAM) | -3-2-2   | Snarf    |

| Page DRAM (70ns) Pipelined  | -4-4-4   | -3-3-4-4 |

| EDO DRAM (60ns) Pipelined   | -5-3-3-3 | -3-3-3-3 |

#### Typical PCI to Memory Performance at 66 MHz CPU Clock and 33MHz PCI Clock

| Read  | 8-1-1-1 -1-1-1-1 7-1-1-1 -1-1-1-1 7-1-1-1 -1-1-1-1                  |

|-------|---------------------------------------------------------------------|

| Write | 5-1-1-1 -3-1-1-1 3-1-1-1 -3-1-1-1 3-1-1-1 -3-1-1-1 3-1-1-1 -3-1-1-1 |

#### **Features**

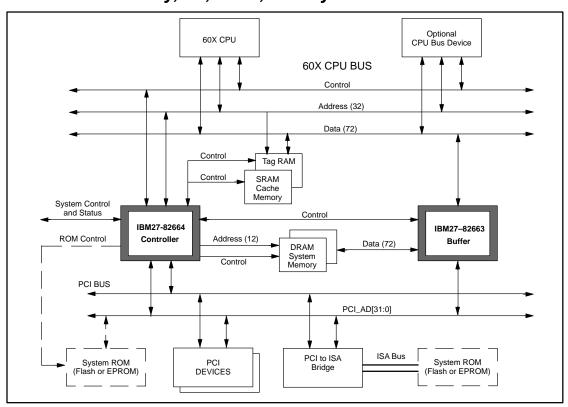

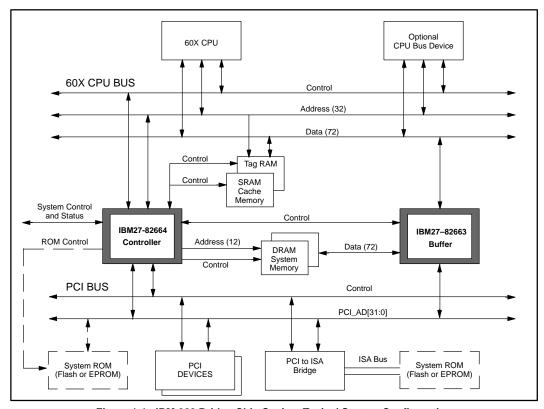

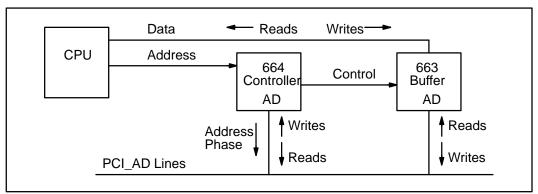

The IBM27-82660 PowerPC to PCI Bridge (the 660 Bridge) interfaces the PowerPC 60x bus to the PCI bus, DRAM, and ROM, controls SRAM and tagRAM to form an L2 cache, and provides the system central resource. The 660 Bridge is PowerPC Reference Platform compliant, and includes the IBM27-82663 data buffer, and the IBM27-82664 controller.

#### General

- PowerPC Reference Platform 1.0/1.1

- Extensive programmability

- Flexible & programmable error handling

- Low cost plastic quad flat packs

- Dual split bus structure CPU–PCI

- Bi-Endian operation

#### CPU

- PowerPC 601, 603, 603e(v), 604, & 604e(v) families

- Up to 2 CPUs at 66MHz on the CPU bus

- · Address pipelining

- MCP# & TEA#/INT# error reporting

- No-DRTRY#/Fast-L2 mode support.

#### PCI

- PCI 2.0/2.1, 33MHz, 3.3v/5v

- Memory accesses snooped to L1 & L2

- ISA master support

- PCI resource locking

- Type 0 & type 1 configuration cycles.

#### DRAM

- ECC or parity DRAM error checking

- Page mode or EDO DRAM

- Up to 1G DRAM with 168-pin DIMMs

- Up to 1G DRAM with 72-pin SIMMs

- Up to 8 memory banks

- Extensive programmability & flexibility

- · Onboard refresh timer/counter.

#### **L2 Cache Controller**

- Look aside, direct mapped, write through

- 256k, 512k or 1M SRAM support

- Sync or asynch SRAM & tagRAM

- Can be disabled.

#### **ROM**

- Up to 2M of ROM

- Flash ROM read, write, and lock-out

- 8 to 64 bit conversion on reads

- Single-beat & burst reads.

## The IBM 660 Bridge

## **PowerPC**<sup>™</sup>

|  |  |   |  |  |  |  |  |  |  |  |  |  |   | _        |

|--|--|---|--|--|--|--|--|--|--|--|--|--|---|----------|

|  |  |   |  |  |  |  |  |  |  |  |  |  |   |          |

|  |  |   |  |  |  |  |  |  |  |  |  |  |   |          |

|  |  |   |  |  |  |  |  |  |  |  |  |  |   |          |

|  |  |   |  |  |  |  |  |  |  |  |  |  |   |          |

|  |  |   |  |  |  |  |  |  |  |  |  |  |   |          |

|  |  |   |  |  |  |  |  |  |  |  |  |  |   |          |

|  |  |   |  |  |  |  |  |  |  |  |  |  |   |          |

|  |  |   |  |  |  |  |  |  |  |  |  |  |   |          |

|  |  |   |  |  |  |  |  |  |  |  |  |  |   |          |

|  |  |   |  |  |  |  |  |  |  |  |  |  |   |          |

|  |  |   |  |  |  |  |  |  |  |  |  |  |   |          |

|  |  |   |  |  |  |  |  |  |  |  |  |  |   |          |

|  |  |   |  |  |  |  |  |  |  |  |  |  |   |          |

|  |  |   |  |  |  |  |  |  |  |  |  |  |   |          |

|  |  |   |  |  |  |  |  |  |  |  |  |  |   | $\dashv$ |

|  |  |   |  |  |  |  |  |  |  |  |  |  | - | $\dashv$ |

|  |  |   |  |  |  |  |  |  |  |  |  |  |   |          |

|  |  |   |  |  |  |  |  |  |  |  |  |  |   |          |

|  |  |   |  |  |  |  |  |  |  |  |  |  |   |          |

|  |  |   |  |  |  |  |  |  |  |  |  |  |   |          |

|  |  |   |  |  |  |  |  |  |  |  |  |  |   | _        |

|  |  |   |  |  |  |  |  |  |  |  |  |  |   |          |

|  |  |   |  |  |  |  |  |  |  |  |  |  |   |          |

|  |  |   |  |  |  |  |  |  |  |  |  |  |   |          |

|  |  |   |  |  |  |  |  |  |  |  |  |  |   |          |

|  |  | l |  |  |  |  |  |  |  |  |  |  |   |          |

|  |  |   |  |  |  |  |  |  |  |  |  |  |   | —        |

|  |  |   |  |  |  |  |  |  |  |  |  |  |   |          |

|  |  |   |  |  |  |  |  |  |  |  |  |  |   |          |

|  |  |   |  |  |  |  |  |  |  |  |  |  |   |          |

|  |  |   |  |  |  |  |  |  |  |  |  |  |   | _        |

|  |  |   |  |  |  |  |  |  |  |  |  |  |   |          |

|  |  |   |  |  |  |  |  |  |  |  |  |  |   |          |

|  |  |   |  |  |  |  |  |  |  |  |  |  |   |          |

|  |  |   |  |  |  |  |  |  |  |  |  |  |   |          |

|  |  |   |  |  |  |  |  |  |  |  |  |  |   |          |

|  |  |   |  |  |  |  |  |  |  |  |  |  |   | _        |

|  |  |   |  |  |  |  |  |  |  |  |  |  |   |          |

|  |  |   |  |  |  |  |  |  |  |  |  |  |   |          |

|  |  |   |  |  |  |  |  |  |  |  |  |  |   |          |

|  |  |   |  |  |  |  |  |  |  |  |  |  |   |          |

|  |  |   |  |  |  |  |  |  |  |  |  |  |   |          |

|  |  |   |  |  |  |  |  |  |  |  |  |  |   |          |

| Section 1 | Overview                                   |

|-----------|--------------------------------------------|

| 1.1       | Packaging and Technology 1                 |

| 1.2       | Microprocessor Support                     |

| 1.3       | L2 Cache Controller                        |

| 1.4       | PCI Expansion Bus                          |

| 1.5       | Memory Controller                          |

| 1.6       | System ROM Controller                      |

| 1.7       | The Bridge Control Register Set 4          |

| 1.8       | Interrupt and Exception Handler 4          |

| 1.9       | Part Identification, IBM27-82660           |

| 1.10      | Improvements Over 650 Bridge 5             |

| 1.11      | Chipset Changes From Prerelease Versions 5 |

| 1.11.1    | CPU_RDL_OPEN Resistor                      |

| 1.11.2    | Parity Error Detection 5                   |

| 1.11.3    | ECIWX/ECOWX With 603                       |

| 1.11.4    | Error Simulation Registers                 |

| 1.11.5    | DRAM Performance 6                         |

| 1.11.6    | CAS# Pulse Width 6                         |

| 1.11.7    | CPU:PCI Bus Ratio 6                        |

| 1.11.8    | Parking the PCI Bus on the 660 6           |

| 1.11.9    | CPU Data Bus Parity With 64-Bit L2 7       |

| 1.11.10   | ECC Single-Bit Error Counter BCR(B8h)      |

| 1.11.11   | 663 Pinout 7                               |

| 1.11.12   | Added Signals 7                            |

| 1.11.13   | Remote ROM                                 |

| 1.11.14   | Power Management 7                         |

| 1.11.15   | VI Curves 7                                |

| 1.11.16   | CPU Data Bus Resistors                     |

| Section 2 | Pin Descriptions9                          |

| 2.1       | Signal Description Table                   |

| 2.2       | CPU_RDL_OPEN Resistor                      |

| Section 3 | 3 CPU Bus21                                |

| 3.1       | Transfer Type Decoding                     |

| 3.2       | CPU Bus Address Mapping                    |

| 3.3       | CPU to Memory Transfers                    |

|           |                                            |

## **PowerPC**<sup>™</sup>

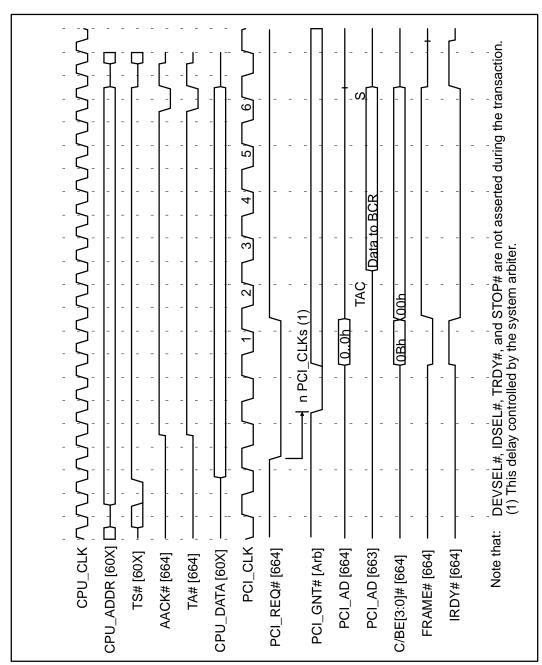

| 3.4       | CPU to PCI Transactions                                      | 24   |

|-----------|--------------------------------------------------------------|------|

| 3.4.1     | CPU to PCI Read                                              |      |

| 3.4.2     | CPU to PCI Write                                             | 25   |

| 3.4.2.1   | Eight-Byte Writes to the PCI (Memory and I/O)                |      |

| 3.4.3     | PCI Retry                                                    |      |

| 3.4.4     | PCI FRAME#                                                   | 25   |

| 3.4.5     | CPU to PCI Configuration                                     | 25   |

| 3.4.5.1   | PCI Type 0 Configuration Transaction (650 Compatible)        | 26   |

| 3.4.5.2   | PCI Type 0 Configuration Transaction (CFC/CF8)               | 26   |

| 3.4.6     | CPU to PCI Interrupt Acknowledge Transaction                 | 26   |

| 3.5       | CPU to ROM                                                   |      |

| 3.6       | CPU to BCR Transfers                                         | 27   |

| 3.7       | CPU to ISA I/O                                               | . 27 |

| 3.7.1     | Contiguous I/O Mode Address Mapping                          | 27   |

| 3.7.2     | Non-Contiguous I/O Mode Address Mapping                      | 28   |

| 3.7.3     | Final I/O Address Formation                                  |      |

| 3.8       | CPU Bus Masters                                              | 30   |

| 3.8.1     | External L2 as a CPU Bus Master                              | 30   |

| 3.9       | CPU Bus Targets                                              | 31   |

| 3.10      | CPU Bus Parity                                               | 31   |

| 3.11      | CPU Bus Arbitration                                          | 32   |

| 3.11.1    | Arbiter Rules                                                | 32   |

| 3.12      | Broadcast Snoop Details                                      | 34   |

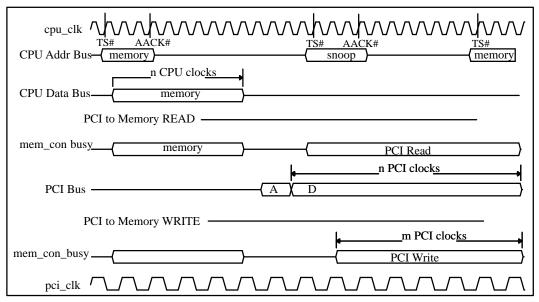

| 3.12.1    | Snoop Cycles From CPU Bus Idle                               | 35   |

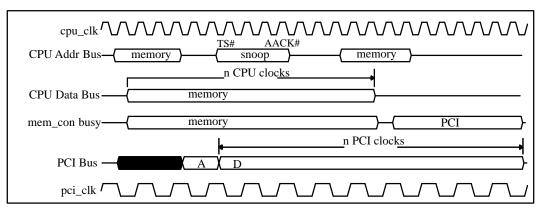

| 3.12.2    | Pipelined Snoop Cycle Following a CPU Bus Transfer           | 36   |

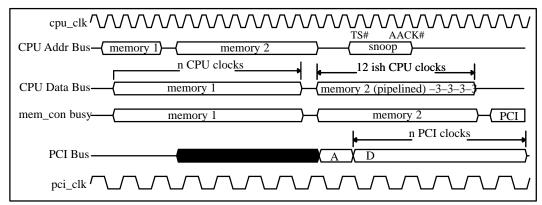

| 3.12.3    | Pipelined Snoop Cycle Following a Pipelined CPU Bus Transfer | 36   |

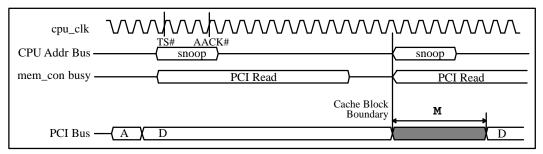

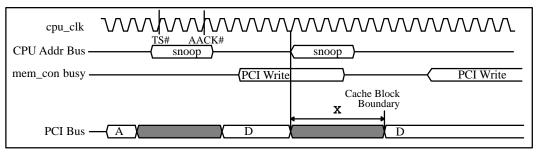

| 3.12.4    | PCI Bus Snoop On Block Boundary During a PCI Burst Read      | 37   |

| 3.12.5    | PCI Bus Snoop On Block Boundary During a PCI Burst Write     | 37   |

| 3.13      | Related Bridge Control Registers                             | 38   |

| Section 4 | 4 PCI Bus                                                    | 39   |

| 4.1       | PCI Arbitration                                              |      |

| 4.2       | PCI Lock                                                     |      |

| 4.2.1     | PCI Busmaster Locks                                          | 39   |

| 4.2.2     | CPU Bus Locking                                              |      |

| 4.3       | 660 (Target) Response by PCI Bus Command                     |      |

| 4.4       | 660 (Target) Response by PCI Memory Address                  |      |

| 4.5       | PCI Access to System Memory                                  |      |

| 4.5.1     | Memory Access Range and Limitations                          |      |

| 4.5.2     | ISA Master Transactions                                      |      |

| 4.5.3     | Memory Access Sequence                                       |      |

| 4.5.3.1   | Snooping                                                     |      |

| 4.5.3.2   | Writes                                                       |      |

|           |                                                              |      |

## **PowerPC**

| 4.5.3.3      | Reads                                               | . 43 |

|--------------|-----------------------------------------------------|------|

| 4.5.4        | PCI to Memory Burst Transfers                       | . 43 |

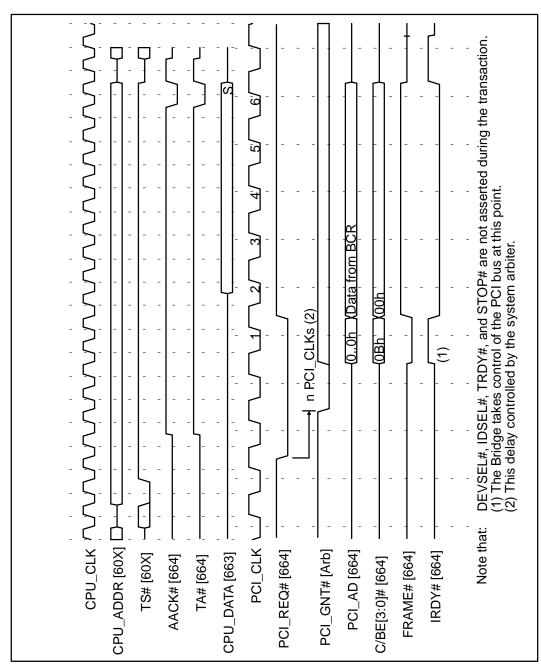

| 4.5.4.1      | Detailed Read Burst Sequence Timing                 | . 43 |

| 4.5.4.2      | Detailed Write Burst Sequence Timing                |      |

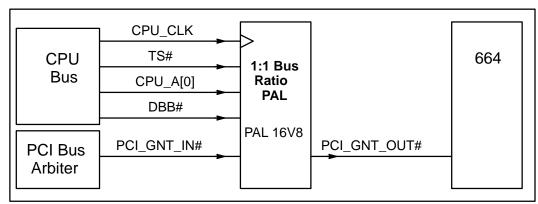

| 4.6          | 1:1 CPU:PCI Bus Ratio Operation                     | . 46 |

| 4.6.1        | 1:1 PAL Connectivity                                | . 47 |

| 4.6.2        | 1:1 PAL Equations                                   | . 48 |

| 4.7          | Related Bridge Control Registers                    |      |

| Section 4    | 5 DRAM                                              | 51   |

| 5.1          | Features and Supported Devices                      |      |

| 5.1.1        | SIMM Nomenclature                                   |      |

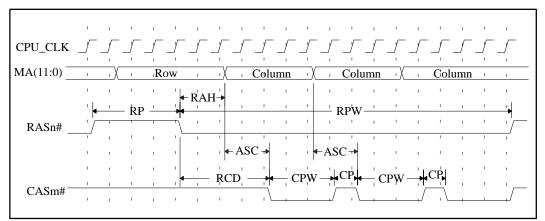

| 5.1.2        | DRAM Timing                                         |      |

| 5.1.2        | DRAM Error Checking                                 |      |

| 5.1.3        | DRAM Performance                                    |      |

| 5.2<br>5.2.1 |                                                     |      |

| 5.2.1.1      | Memory Timing Parameters                            |      |

| 5.2.1.1      | Memory Timing Register 2                            |      |

|              | Memory Timing Register 2                            |      |

| 5.2.1.3      | RAS# Watchdog Timer BCR                             |      |

| 5.2.2        | General Case DRAM Timing Calculations               |      |

| 5.2.3        | General Case DRAM Timing Examples                   |      |

| 5.2.3.1      | 70ns DRAM Calculations                              |      |

| 5.2.3.2      | 60ns DRAM Calculations                              |      |

| 5.2.3.3      | 50ns DRAM Calculations                              |      |

| 5.2.3.4      | 60ns EDO DRAM Calculations                          |      |

| 5.2.3.5      | Aggressive Timing Summary                           |      |

| 5.2.3.6      | Conservative Timing Summary                         |      |

| 5.2.4        | Special Case Memory Controller Operation            |      |

| 5.2.4.1      | Required Conditions for Special Case Operation      |      |

| 5.2.4.2      | Avoiding The Special Case                           |      |

| 5.2.4.3      | Special Case Option 1 – Disable Page Mode           |      |

| 5.2.4.4      | Special Case Option 2 – Change the DRAM Timing      |      |

| 5.2.4.5      | Special Case Option 3 – Performance Enhancement PAL |      |

| 5.2.4.6      | Performance Enhancement PAL Design                  | . 67 |

| 5.2.5        | Page Hit and Page Miss                              |      |

| 5.2.6        | CPU to Memory Access Pipelining                     | . 71 |

| 5.2.7        | Extended Data Out (EDO) DRAM                        | . 71 |

| 5.3          | System Memory Addressing                            | . 72 |

| 5.3.1        | DRAM Logical Organization                           | . 72 |

| 5.3.2        | SIMM Topologies                                     | . 73 |

| 5.3.3        | Row and Column Address Generation                   | . 74 |

| 5.3.4        | DRAM Pages                                          |      |

| 5.3.5        | Supported Transfer Sizes and Alignments             | . 75 |

## **PowerPC**<sup>™</sup>

| 75       |

|----------|

| 75       |

| 76       |

| 76       |

| 77       |

| 77       |

| 78       |

| 78       |

| 79       |

| 79       |

| 80       |

| 81       |

| 81       |

| 81       |

| 82       |

| 82       |

| 83       |

| 84       |

| 84       |

| 84       |

| 85       |

| 85       |

| 85       |

| 87       |

| 88       |

| 89       |

| 90       |

| 91       |

| 91       |

| 91       |

| 91       |

| 91       |

| 92       |

| 92       |

| 93       |

| 93       |

| 93       |

| 93       |

|          |

| 93       |

| 93<br>93 |

| 93       |

|          |

## PowerPC"

| 6.4     | Error Checking Support                    | 95  |

|---------|-------------------------------------------|-----|

| 6.5     | External L2 Cache Operation               |     |

| 6.6     | TagRAM                                    |     |

| 6.6.1   | TAG_MATCH                                 |     |

| 6.7     | SRAM                                      |     |

| 6.7.1   | Synchronous                               |     |

| 6.7.2   | Asynchronous                              |     |

| 6.7.3   | Dual (Sync and Async) Capable Systems     |     |

| 6.8     | SRAM and TagRAM Connections               |     |

| 6.9     | L2 Bridge Control Registers               |     |

| 6.9.1   | L2 Invalidate BCR                         |     |

| 6.9.2   | L2 Error Status BCR                       |     |

| 6.9.3   | L2 Parity Error Read and Clear BCR        |     |

| 6.9.4   | Cache Status Register                     |     |

| 6.9.5   | Other L2-Related BCRs                     |     |

| 0.0.0   |                                           |     |

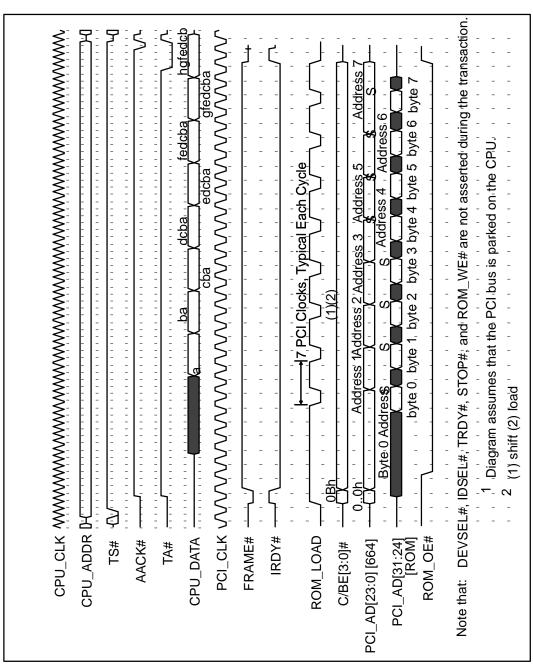

| Section | 17 ROM                                    |     |

| 7.1     | Direct-Attach ROM Mode                    |     |

| 7.1.1   | ROM Reads                                 |     |

| 7.1.1.1 | ROM Read Sequence                         |     |

| 7.1.1.2 | Address, Transfer Size, and Alignment     |     |

| 7.1.1.3 | Endian Mode Considerations                | 110 |

| 7.1.1.4 | 4-Byte Reads                              | 111 |

| 7.1.2   | ROM Writes                                | 111 |

| 7.1.2.1 | ROM Write Sequence                        | 111 |

| 7.1.2.2 | Write Protection                          | 111 |

| 7.1.2.3 | Data Flow In Little-Endian Mode           | 112 |

| 7.1.2.4 | Data Flow In Big-Endian Mode              | 112 |

| 7.2     | Remote ROM Mode                           | 113 |

| 7.2.1   | Remote ROM Reads                          | 114 |

| 7.2.1.1 | Remote ROM Read Sequence                  | 114 |

| 7.2.1.2 | Address, Transfer Size, and Alignment     | 117 |

| 7.2.1.3 | Burst Reads                               | 117 |

| 7.2.1.4 | Endian Mode Considerations                | 117 |

| 7.2.1.5 | 4-Byte Reads                              | 118 |

| 7.2.2   | Remote ROM Writes                         | 118 |

| 7.2.2.1 | Write Sequence                            | 118 |

| 7.2.2.2 | Write Protection                          |     |

| 7.2.2.3 | Address, Size, Alignment, and Endian Mode | 118 |

| 7.3     | Related Bridge Control Registers          |     |

| 7.3.1   | ROM Write Bridge Control Register         |     |

| 7.3.2   | Direct-Attach ROM Lockout BCR             |     |

| 7.3.3   | Remote ROM Lockout Bit                    |     |

|         |                                           | ·   |

## **PowerPC**<sup>™</sup>

| 7.3.4   | Other Related BCRs                               | 121 |

|---------|--------------------------------------------------|-----|

| 7.4     | Programming the ROM Boot For 601 Burst Reads     | 122 |

| Section | 8 Exceptions: Resets, Interrupts, Errors, & Test | 123 |

| 8.1     | Resets                                           |     |

| 8.1.1   | Reset Timing                                     |     |

| 8.1.2   | Reset State of 660 Pins                          |     |

| 8.1.3   | Configuration Strapping                          | 125 |

| 8.1.4   | Deterministic Operation (Lockstep Applications)  | 126 |

| 8.2     | Interrupts                                       | 127 |

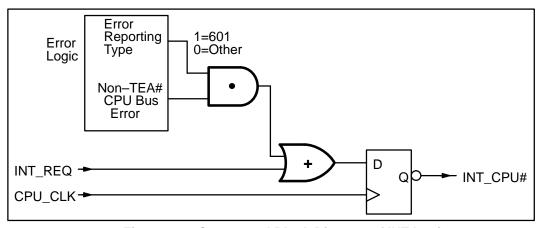

| 8.2.1   | INT_REQ and INT_CPU#                             | 127 |

| 8.2.2   | NMI_REQ                                          |     |

| 8.2.3   | Interrupt-Related Bridge Control Registers       | 127 |

| 8.3     | Error Handling Protocol                          | 128 |

| 8.3.1   | NMI Errors                                       | 128 |

| 8.3.1.1 | Error Handling Protocol                          | 128 |

| 8.3.2   | CPU Bus Related Errors                           | 129 |

| 8.3.2.1 | Error Types                                      | 129 |

| 8.3.2.2 | Error Handling Protocol                          |     |

| 8.3.3   | PCI Bus Related Errors                           |     |

| 8.3.3.1 | Error Types                                      |     |

| 8.3.3.2 | Error Handling Protocol                          |     |

| 8.3.3.3 | PCI Bus Data Parity Errors                       |     |

| 8.4     | Error Reporting Protocol                         |     |

| 8.4.1   | Error Reporting With MCP#                        |     |

| 8.4.2   | Error Reporting With TEA#                        |     |

| 8.4.3   | Error Reporting to 601 CPU                       |     |

| 8.4.4   | Error Reporting With PCI_SERR#                   |     |

| 8.4.5   | Error Reporting With PCI_PERR#                   |     |

| 8.5     | Error Handling Details by Error Type             |     |

| 8.5.1   | CPU Bus Transfer Type or Size Error              |     |

| 8.5.2   | CPU Bus XATS# Asserted Error                     |     |

| 8.5.3   | CPU Data Bus Parity Error                        |     |

| 8.5.4   | CPU Bus Write to Locked Flash                    |     |

| 8.5.5   | Memory Select Error                              |     |

| 8.5.6   | System Memory Parity Error                       |     |

| 8.5.7   | System Memory Single-Bit ECC Error               |     |

| 8.5.8   | System Memory Multi-Bit ECC Error                |     |

| 8.5.9   | L2 Cache Parity Error                            |     |

| 8.5.10  | PCI Bus Data Parity Error While PCI Master       |     |

| 8.5.11  | PCI Target Abort Received While PCI Master       |     |

| 8.5.12  | PCI Master Abort Detected While PCI Master       |     |

| 8.5.13  | PCI Address Bus Parity Error While PCI Target    | 138 |

## **PowerPC**

| 8.5.14  | PCI Bus Data Parity Error While PCI Target | 139 |

|---------|--------------------------------------------|-----|

| 8.5.15  | NMI REQ Asserted Error                     |     |

| 8.5.16  | Error-Related Bridge Control Registers     |     |

| 8.6     | Test Modes                                 |     |

| 8.6.1   | LSSD Test Mode                             |     |

| 8.6.2   | MIO Test Mode                              |     |

| Section | 9 Endian Mode                              | 145 |

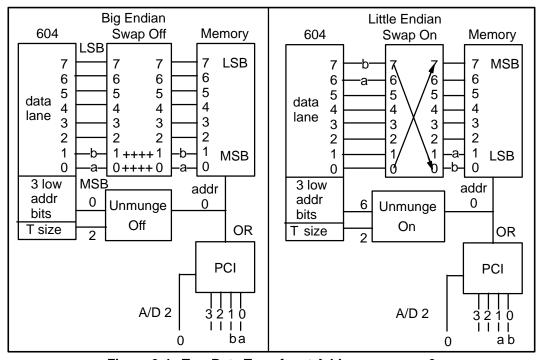

| 9.1     | What the CPU Does                          |     |

| 9.1.1   | The CPU Address Munge                      |     |

| 9.1.2   | The CPU Data Shift                         |     |

| 9.2     | What the 660 Does                          |     |

| 9.2.1   | The 660 Address Unmunge                    |     |

| 9.2.2   | The 660 Data Swapper                       |     |

| 9.3     | Bit Ordering Within Bytes                  |     |

| 9.4     | Byte Swap Instructions                     |     |

| 9.5     | CPU Alignment Exceptions In LE Mode        |     |

| 9.6     | Endian Mode Examples                       |     |

| 9.6.1   | One Byte Transfers                         |     |

| 9.6.2   | Two Byte Transfers                         |     |

| 9.6.3   | Four Byte Transfers                        |     |

| 9.6.4   | Three byte Transfers                       |     |

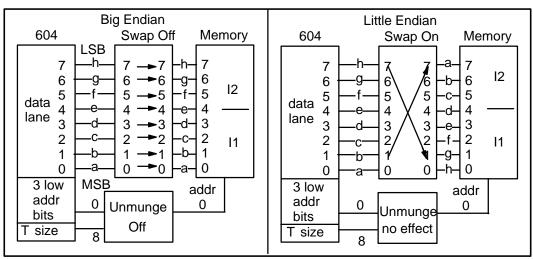

| 9.6.5   | Eight Byte Transfers                       |     |

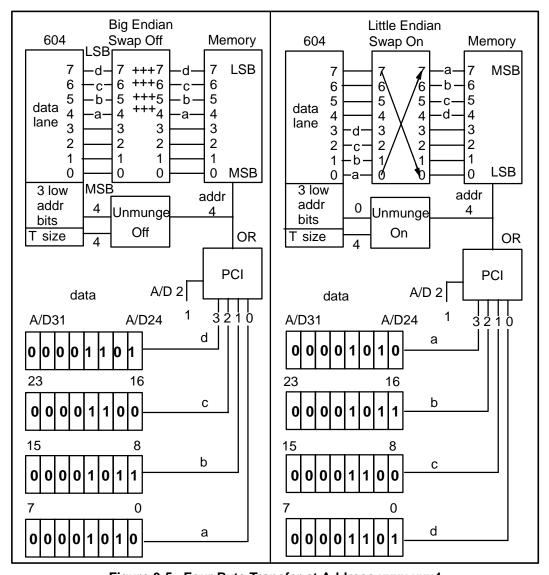

| 9.7     | Endian Mode Flow Oriented Examples         |     |

| 9.7.1   | 1-Byte Example at Address xxxx xxx1        |     |

| 9.7.2   | 2-Byte Example at Address xxxx xxx0        |     |

| 9.7.3   | 4-Byte Example at Address xxxx xxx0        |     |

| 9.7.4   | 8-Byte Example at Address xxxx xxx0        |     |

| 9.8     | Tabular Endian Mode Examples               |     |

| 9.8.1   | One-Byte CPU to Memory Transfer in BE Mode |     |

| 9.8.2   | One-Byte CPU to Memory Transfer in LE Mode |     |

| 9.8.3   | One-Byte CPU to PCI Transfer in BE Mode    |     |

| 9.8.4   | One-Byte CPU to PCI Transfer in LE Mode    |     |

| 9.8.5   | Two-Byte CPU to Memory or PCI Transfer     |     |

| 9.8.6   | Rearranged 2-Byte Transfer Information     |     |

| 9.8.7   | Four-Byte CPU to Memory or PCI Transfer    |     |

| 9.8.8   | Rearranged 4-Byte Transfer Information     |     |

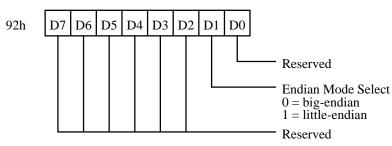

| 9.9     | Changing BE/LE Mode                        |     |

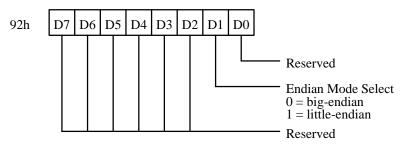

| 9.9.1   | Special Port 92 Mirror BCR                 |     |

| Section | 10 Bridge Control Registers                | 163 |

| 10.1    | Overview                                   |     |

| 10.1.1  | Direct-Access Bridge Control Registers     |     |

|         |                                            |     |

## **PowerPC**<sup>™</sup>

| 10.1.2    | Indexed Bridge Control Register Access |

|-----------|----------------------------------------|

| 10.1.3    | Indexed Bridge Control Registers       |

| 10.2      | Direct-Access BCRs                     |

| 10.2.1    | PCI BCR Transactions                   |

| 10.2.2    | Direct-Access BCR Listing              |

| 10.2.2.1  | Special Port 92 Mirror BCR             |

| 10.2.2.2  | L2 Invalidate BCR                      |

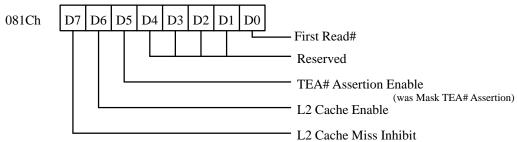

| 10.2.2.3  | System Control 81C BCR                 |

| 10.2.2.4  | Memory Controller Miscellaneous BCR    |

| 10.2.2.5  | Memory Parity Error Status BCR         |

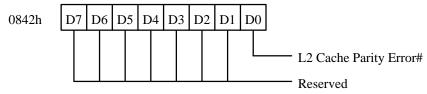

| 10.2.2.6  | L2 Error Status BCR                    |

| 10.2.2.7  | L2 Parity Error Read and Clear BCR     |

| 10.2.2.8  | Unsupported Transfer Type Error BCR    |

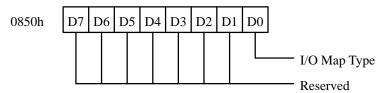

| 10.2.2.9  | I/O Map Type BCR                       |

| 10.2.2.10 | PCI/BCR Configuration Address BCR      |

| 10.2.2.11 | PCI/BCR Configuration Data BCR 174     |

| 10.2.2.12 | PCI Type 0 Configuration Addresses     |

| 10.2.2.13 | System Error Address BCR               |

| 10.2.2.14 | Interrupt Acknowledge BCR              |

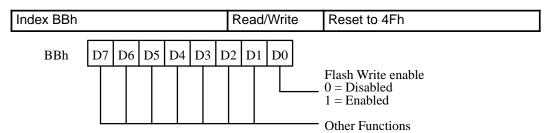

| 10.2.2.15 | ROM Write Bridge Control BCR           |

| 10.2.2.16 | ROM Lockout BCR176                     |

| 10.3      | Indexed BCRs                           |

| 10.3.1    | Indexed BCR Access                     |

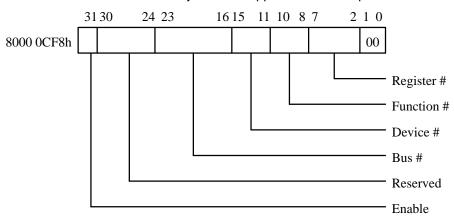

| 10.3.1.1  | PCI/BCR Configuration Address BCR      |

| 10.3.1.2  | PCI/BCR Configuration Data BCR 179     |

| 10.3.2    | Indexed BCR Summary                    |

| 10.3.3    | PCI Vendor ID Register                 |

| 10.3.4    | PCI Device ID Register                 |

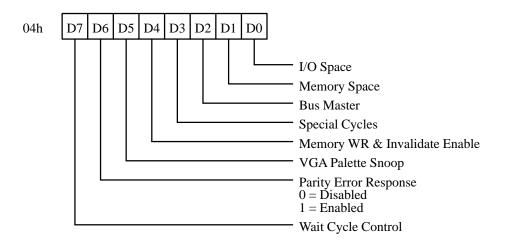

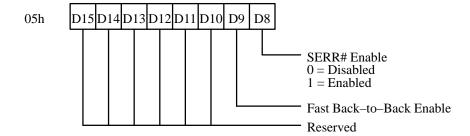

| 10.3.5    | PCI Command Register                   |

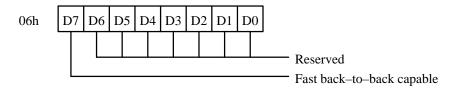

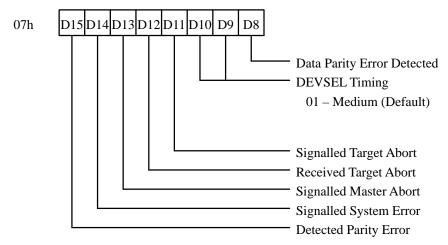

| 10.3.6    | PCI Device Status Register             |

| 10.3.7    | Revision ID                            |

| 10.3.8    | PCI Standard Programming Interface     |

| 10.3.9    | PCI Subclass Code                      |

| 10.3.10   | PCI Class Code                         |

| 10.3.11   | PCI Cache Line Size                    |

| 10.3.12   | PCI Latency Timer                      |

| 10.3.13   | PCI Header Type                        |

| 10.3.14   | PCI Built-in Self-Test (BIST) Control  |

| 10.3.15   | PCI Interrupt Line                     |

| 10.3.16   | PCI Interrupt Pin                      |

| 10.3.17   | PCI MIN_GNT 189                        |

| 10.3.18   | PCI MAX_LAT190                         |

| 10.3.19   | PCI Bus Number                         |

## **PowerPC**

| 10.3.20 | PCI Subordinate Bus Number                        |     |

|---------|---------------------------------------------------|-----|

| 10.3.21 | PCI Disconnect Counter                            | 190 |

| 10.3.22 | PCI Special Cycle Address Register                |     |

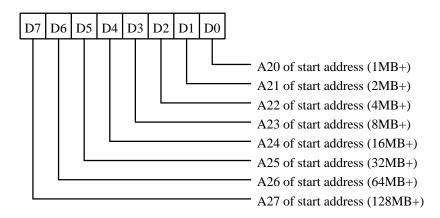

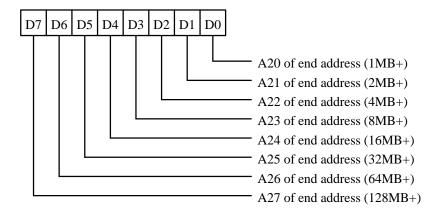

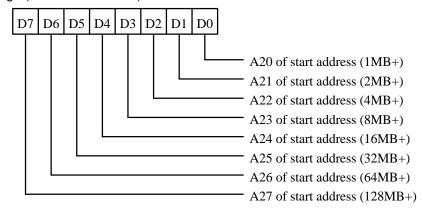

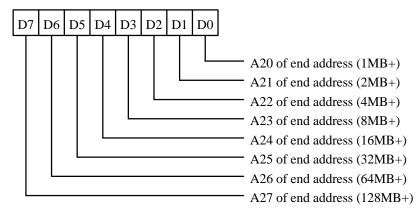

| 10.3.23 | Memory Bank Starting Address                      |     |

| 10.3.24 | Memory Bank Extended Starting Address             | 191 |

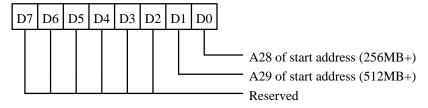

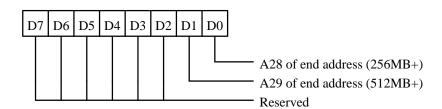

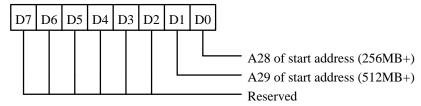

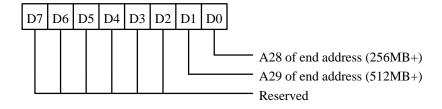

| 10.3.25 | Memory Bank Ending Address                        | 192 |

| 10.3.26 | Memory Bank Extended Ending Address               | 192 |

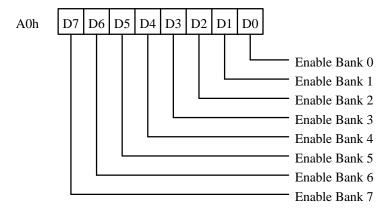

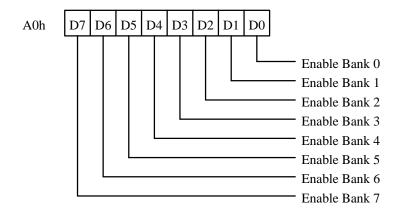

| 10.3.27 | Memory Bank Enable                                |     |

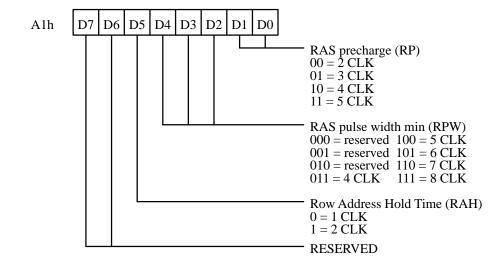

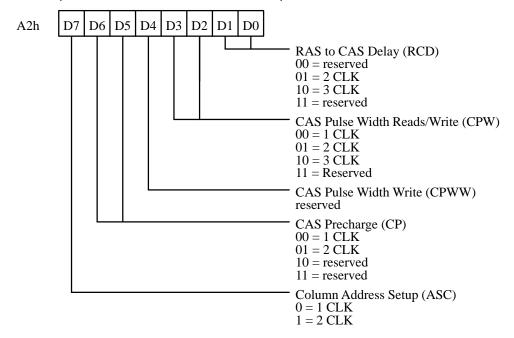

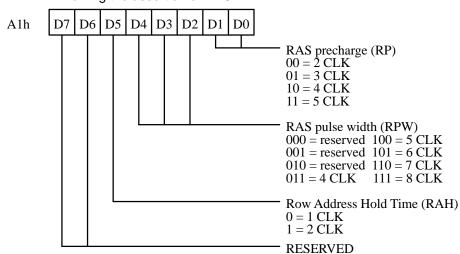

| 10.3.28 | Memory Timing Register 1                          | 194 |

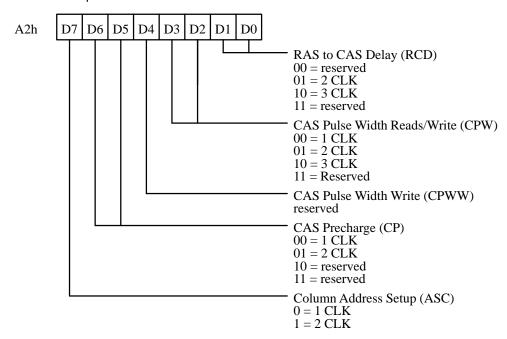

| 10.3.29 | Memory Timing Register 2                          |     |

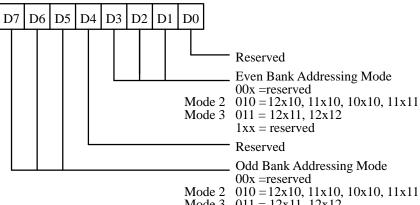

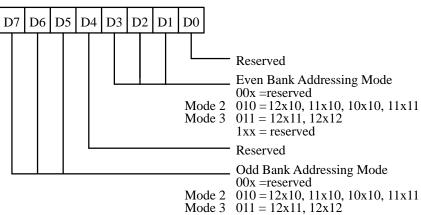

| 10.3.30 | Memory Bank Addressing Mode Registers             | 196 |

| 10.3.31 | Cache Status Register                             | 197 |

| 10.3.32 | RAS# Watchdog Timer Register                      | 197 |

| 10.3.33 | Single-Bit Error Counter Register                 | 198 |

| 10.3.34 | Single-Bit Error Trigger Level Register           | 198 |

| 10.3.35 | Bridge Chip Set Options 1                         | 199 |

| 10.3.36 | Bridge Chip Set Options 2                         | 200 |

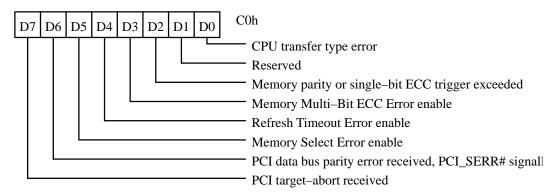

| 10.3.37 | Error Enable 1                                    | 201 |

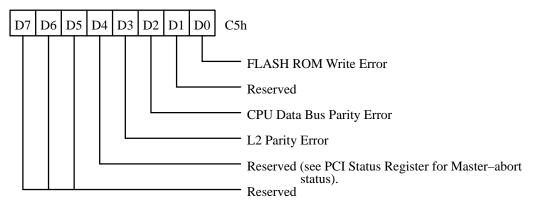

| 10.3.38 | Error Status 1                                    | 202 |

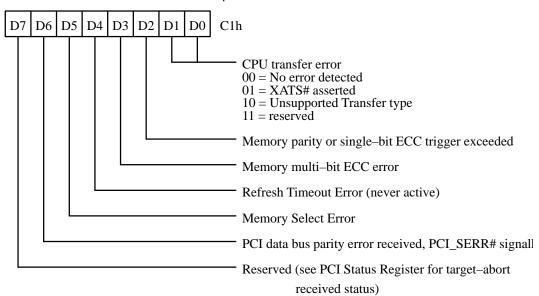

| 10.3.39 | CPU Bus Error Status                              | 203 |

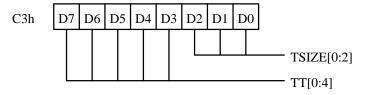

| 10.3.40 | Error Enable 2                                    | 203 |

| 10.3.41 | Error Status 2                                    | 204 |

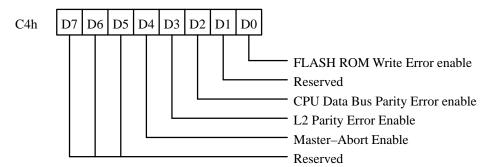

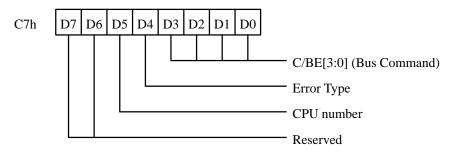

| 10.3.42 | PCI Bus Error Status                              | 205 |

| 10.3.43 | CPU/PCI Error Address                             | 205 |

| 10.3.44 | Single-Bit ECC Error Address                      | 206 |

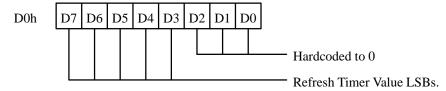

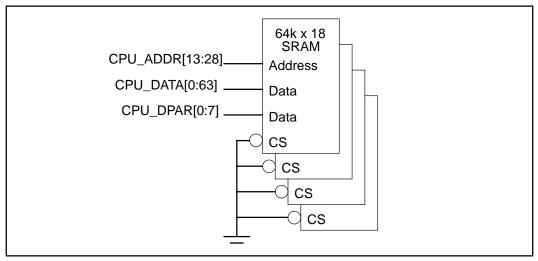

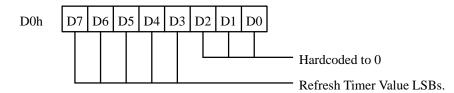

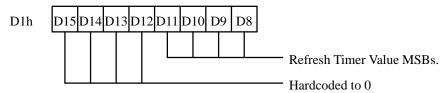

| 10.3.45 | Refresh Timer Divisor Register                    | 206 |

| 10.3.46 | Bridge Chip Set Options 3 Register                | 207 |

| Append  | lix A Timing                                      | 209 |

| A.1     | Timing Conventions                                |     |

| A.1.1   | Board Delays                                      |     |

| A.1.2   | Terms and Definitions                             |     |

| A.1.3   | Signal Switching Levels for Timing Analysis       |     |

| A.1.4   | Input Setup Time                                  |     |

| A.1.5   | Input Hold Time                                   |     |

| A.1.6   | Output Hold Time                                  |     |

| A.1.7   | Output Delay Time                                 |     |

| A.1.8   | Output Enable Time                                |     |

| A.1.9   | Output Tristate Hold Time                         |     |

| A.1.10  | Output Tristate Delay Time                        |     |

| A.2     | Clock Considerations                              |     |

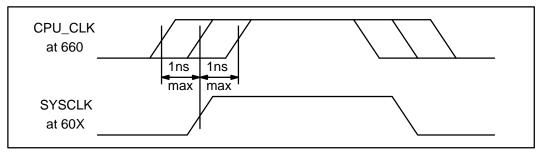

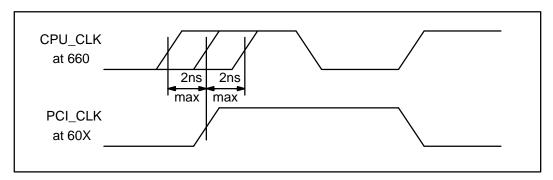

| A.2.1   | 660 Bridge CPU_CLK Skew to the Processor SYSCLK   |     |

| A.2.2   | 663 Buffer CPU_CLK Skew to 664 Controller CPU_CLK |     |

|         |                                                   |     |

## PowerPC \*\*

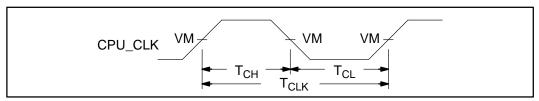

| A.2.3   | CPU_CLK Duty Cycle                                                                      | . 213 |

|---------|-----------------------------------------------------------------------------------------|-------|

| A.2.4   | CPU_CLK to PCI_CLK Skew                                                                 |       |

| A.3     | Asynchronous Paths                                                                      | . 214 |

| A.4     | Power-On Considerations                                                                 | . 214 |

| A.5     | 663 Buffer Timing By Signal                                                             | . 215 |

| A.6     | 664 Controller Timing By Signal                                                         | . 217 |

| A.7     | Detailed Timing Diagrams                                                                | . 220 |

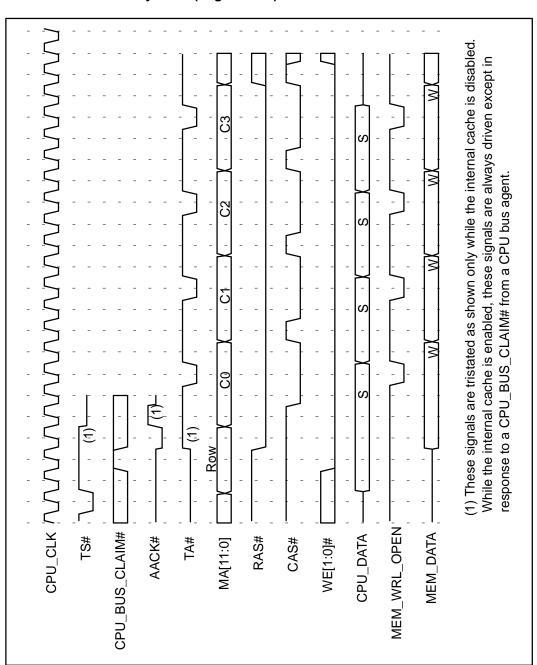

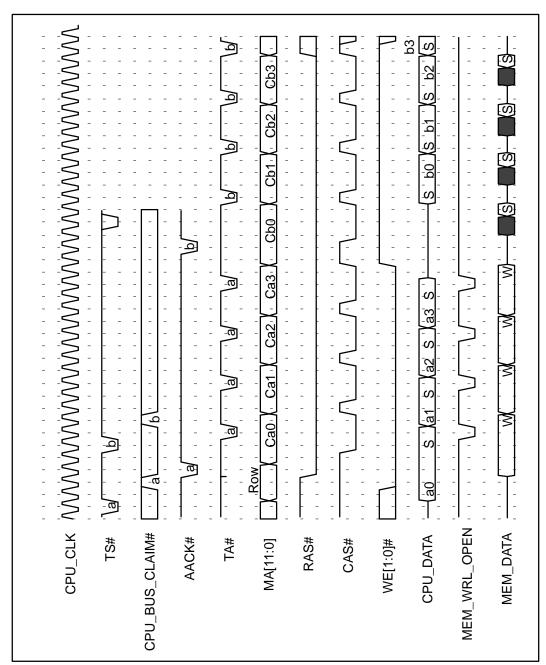

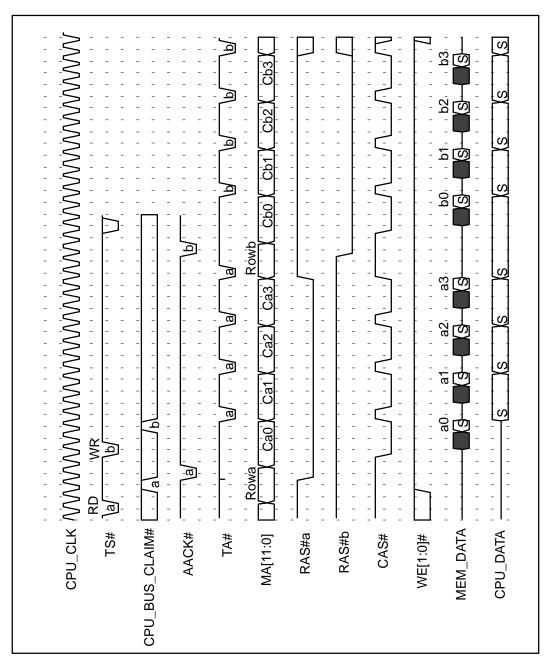

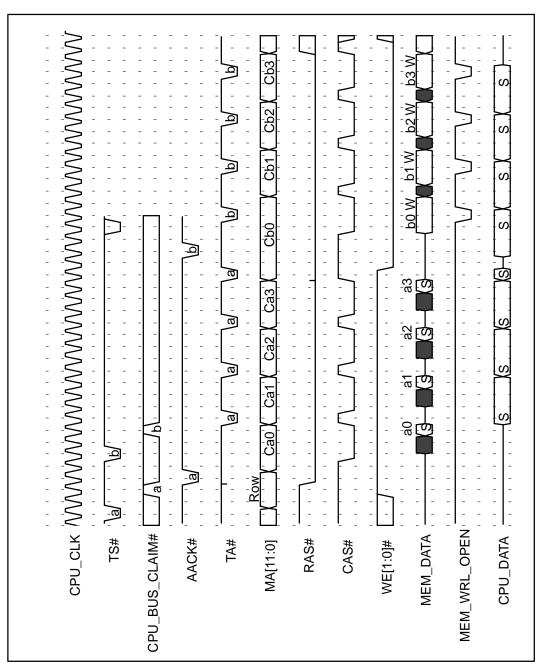

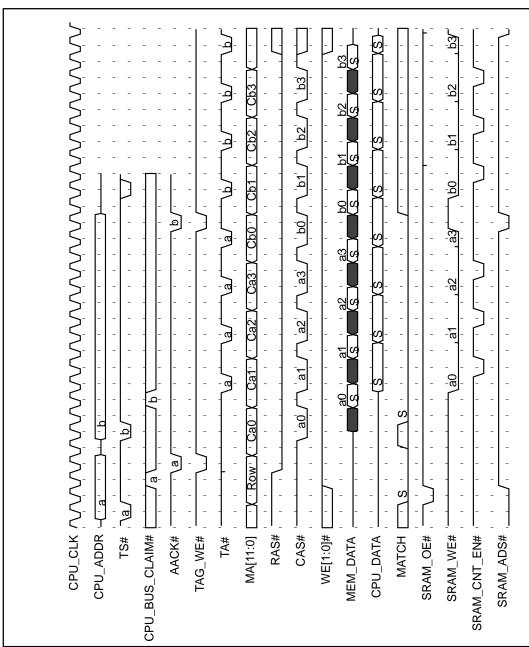

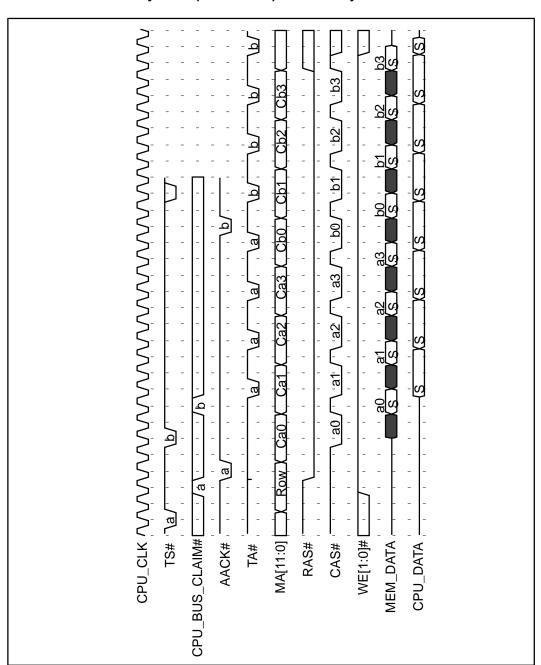

| A.7.1   | CPU to Memory Write (Page DRAM) From Bus Idle                                           | 221   |

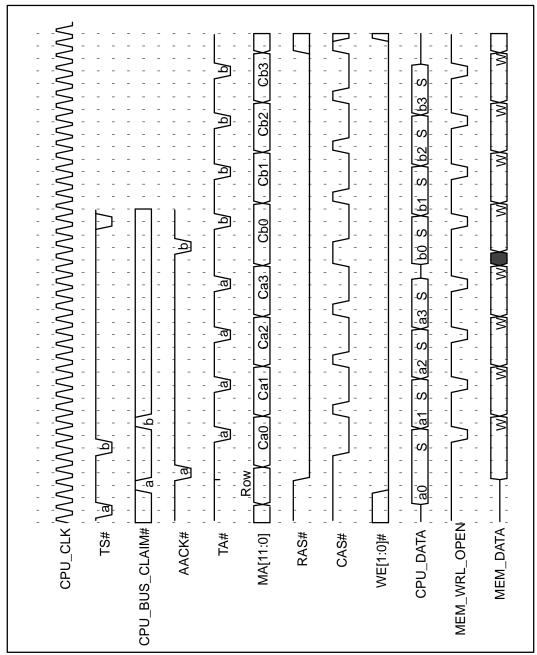

| A.7.2   | CPU to Memory Write (Page DRAM) Followed by Write Hit                                   | 222   |

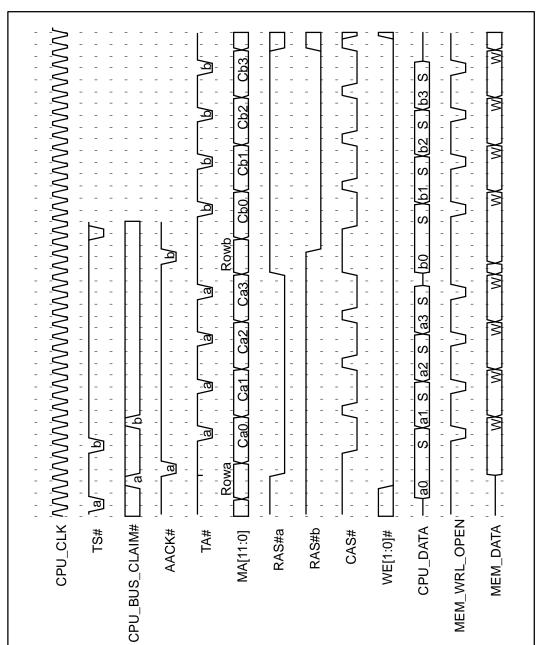

| A.7.3   | CPU to Memory Write (Page DRAM) Followed by Write Page Miss an Bank Miss                | . 223 |

| A.7.4   | CPU to Memory Write (Page DRAM) Followed by Read Hit                                    | 224   |

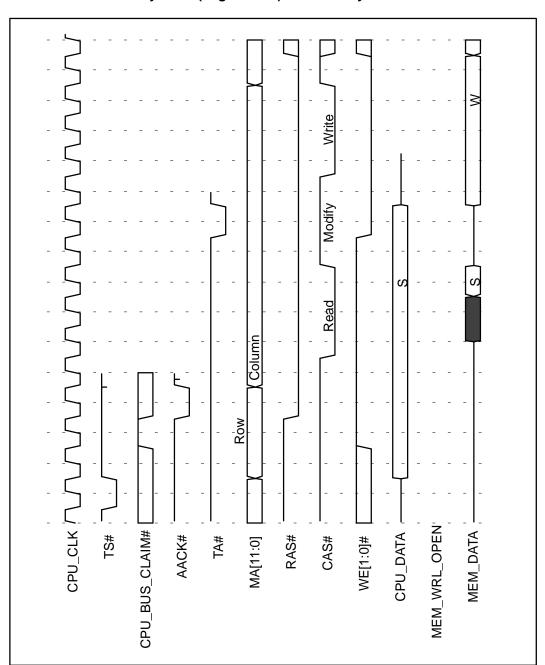

| A.7.5   | CPU to Memory Write (Page DRAM) Read/Modify/Write From Bus Idle                         | . 225 |

| A.7.6   | CPU to Memory Read (Page DRAM) From Bus Idle                                            | 226   |

| A.7.7   | CPU to Memory Read (Page DRAM) Followed by Read Hit                                     | 227   |

| A.7.8   | CPU to Memory Read (Page DRAM) Followed by Read Miss and Bank Miss                      | . 228 |

| A.7.9   | CPU to Memory Read (Page DRAM) Followed by Write Hit                                    | 229   |

| A.7.10  | CPU to Bridge Write of Bridge Control Register                                          | 230   |

| A.7.11  | CPU to Bridge Read of ROM                                                               | 231   |

| A.7.12  | CPU to Bridge Read of Bridge Control Register                                           | 232   |

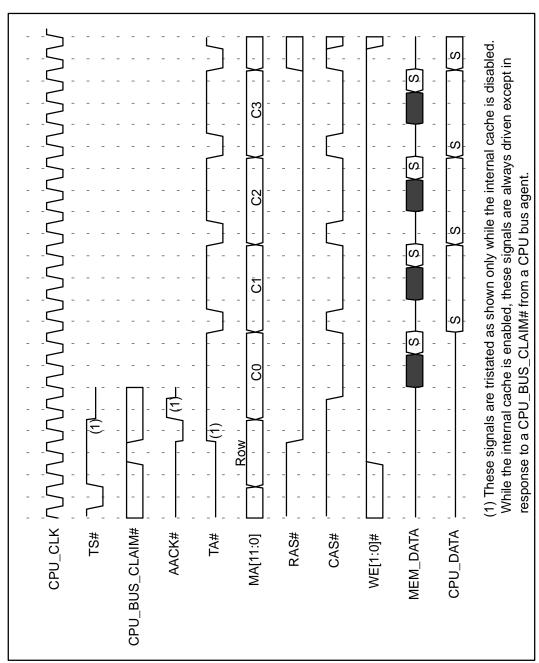

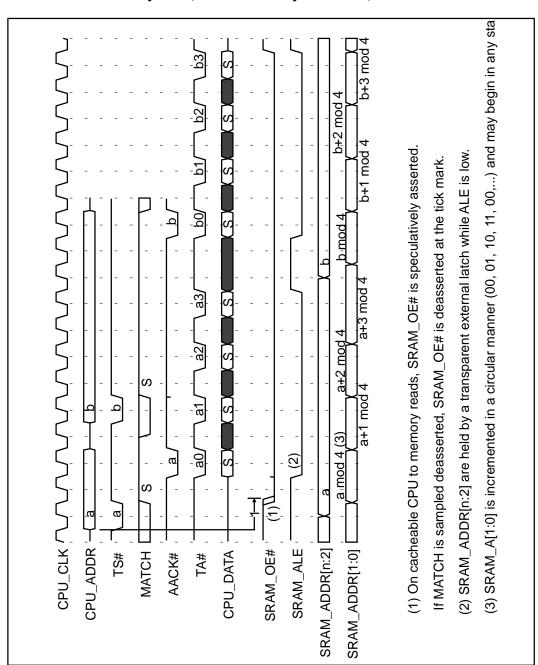

| A.7.13  | CPU to Memory Read, L2 Cache w/Async SRAMS, Hit                                         | 233   |

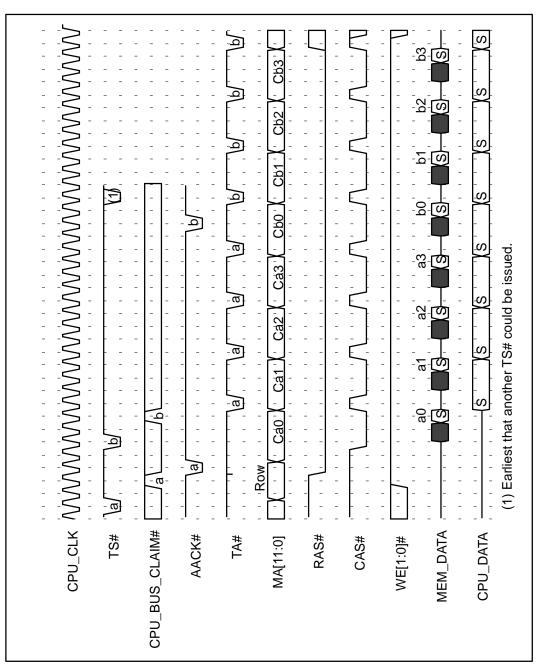

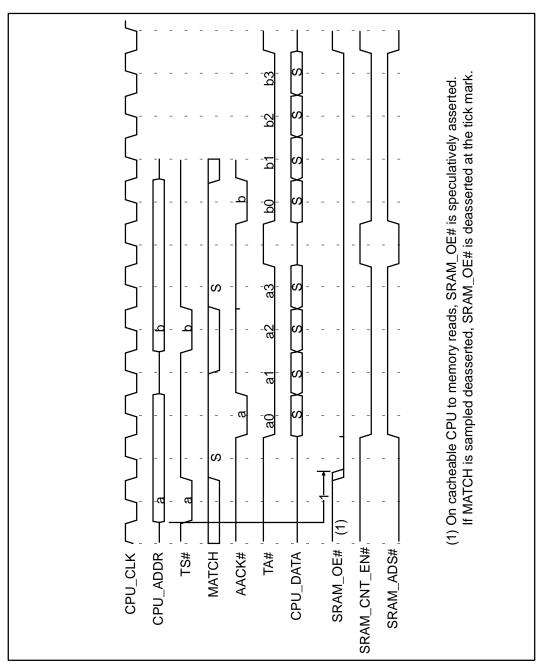

| A.7.14  | CPU to Memory Read, L2 Cache w/Burst SRAMs, Hit                                         |       |

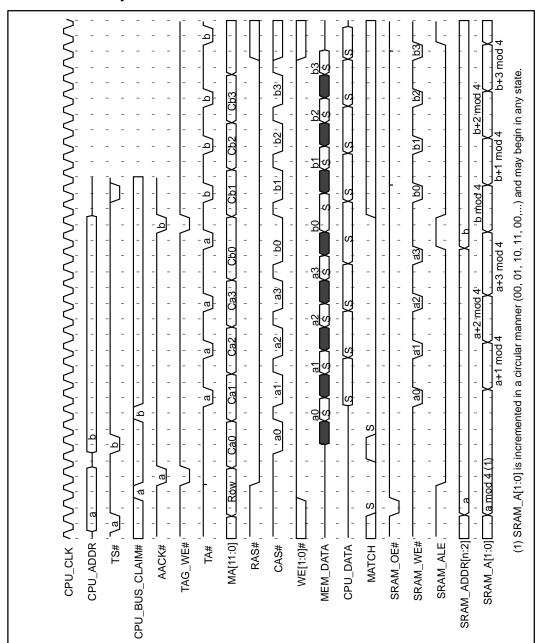

| A.7.15  | CPU to Memory Read (EDO DRAM) Cache Miss Followed by Read H<br>Cache Miss w/Async SRAMs | 235   |

| A.7.16  | CPU to Memory Read (EDO DRAM) Cache Miss Followed by Read H                             | lit   |

| A 7 47  | Cache Miss w/Burst SRAMs                                                                |       |

| A.7.17  | CPU to Memory Read (EDO DRAM) Followed by Read Hit                                      |       |

| Appendi | x B Electrical and Mechanical                                                           |       |

| B.1     | Absolute Maximum Ratings                                                                |       |

| B.2     | Recommended Operating Conditions                                                        |       |

| B.3     | Power Dissipation and Thermal Characteristics                                           |       |

| B.3.1   | Power Dissipation                                                                       |       |

| B.3.2   | Thermal Characteristics                                                                 |       |

| B.4     | Common Characteristics                                                                  |       |

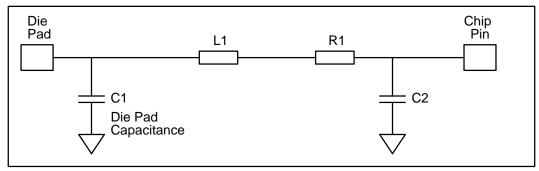

| B.5     | Package and Pin Electrical Characteristics Model                                        |       |

| B.6     | 663 DC Characteristics By Signal                                                        |       |

| B.7     | 664 DC Characteristics By Signal                                                        |       |

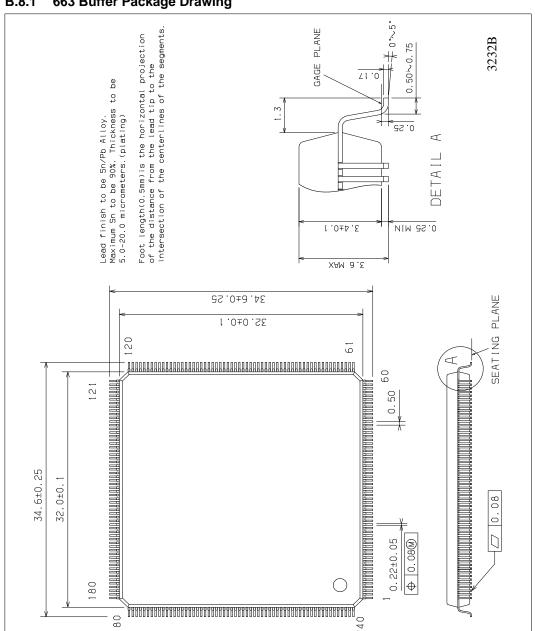

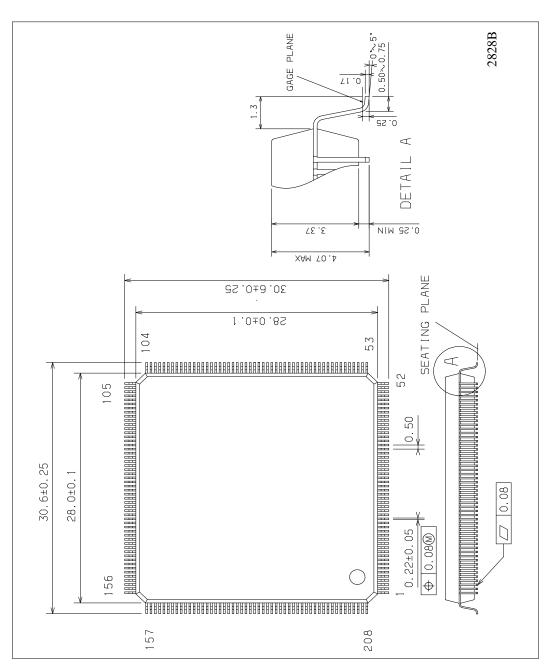

| B.8     | Package Drawings                                                                        |       |

| B.8.1   | 663 Buffer Package Drawing                                                              |       |

| B.8.2   | 664 Controller Package Drawing                                                          |       |

|         | x C Pin Lists                                                                           |       |

| C.1     | 663 Buffer Alphabetic Pin List                                                          | 249   |

## **PowerPC**

### **Table of Contents**

| Contacts | ·                                   | 259 |

|----------|-------------------------------------|-----|

| C.4      | 664 Controller Numeric Pins         | 256 |

|          | 664 Controller Alphabetic Pin Lists |     |

|          | 663 Buffer Numeric Pin List         |     |

|          |                                     |     |

## **Figures**

| Figure 1-1.  | IBM 660 Bridge Chip Set in a Typical System Configuration      | 1   |

|--------------|----------------------------------------------------------------|-----|

| Figure 2-1.  | 660 Bridge Pin Connections                                     |     |

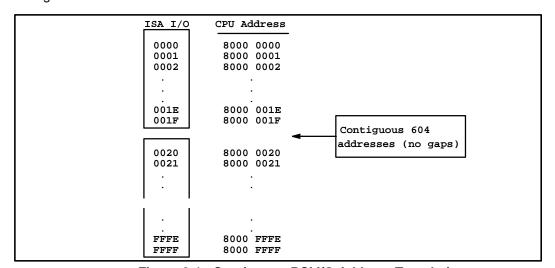

| Figure 3-1.  | Contiguous PCI I/O Address Translation                         |     |

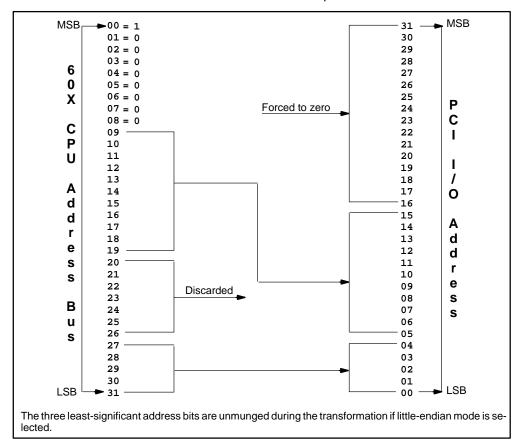

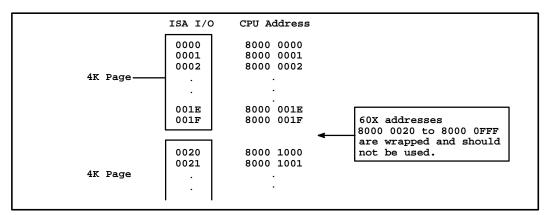

| Figure 3-2.  | Non-Contiguous PCI I/O Address Transformation                  | 28  |

| Figure 3-3.  | Non-Contiguous PCI I/O Address Translation                     | 29  |

| Figure 3-4.  | PCI Bus Snoops From CPU Bus Idle                               |     |

| Figure 3-5.  | Pipelined PCI Bus Snoop Following a CPU Bus Transfer           |     |

| Figure 3-6.  | Pipelined PCI Bus Snoop Following a Pipelined CPU Bus Transfer | 37  |

| Figure 3-7.  | PCI Bus Snoop On Block Boundary During a PCI Burst Read        | 37  |

| Figure 3-8.  | PCI Bus Snoop On Block Boundary During a PCI Burst Write       | 37  |

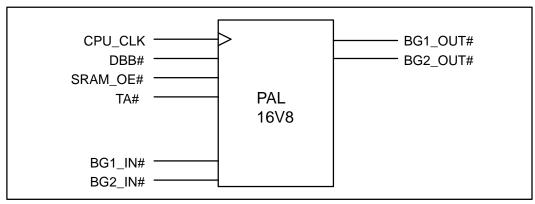

| Figure 4-1.  | PAL                                                            | 47  |

| Figure 5-1.  | CPU to Memory Transfer Timing Parameters                       | 53  |

| Figure 5-2.  | PAL                                                            | 67  |

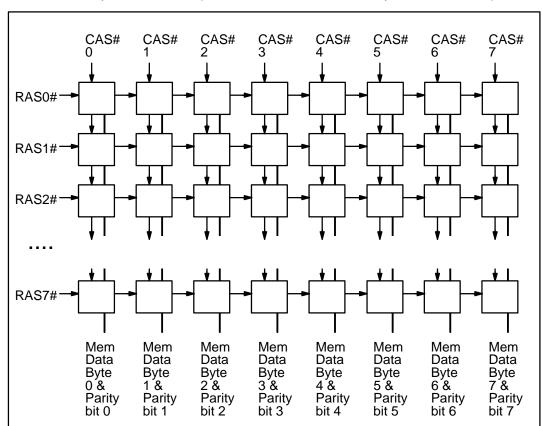

| Figure 5-3.  | DRAM Logical Implementation                                    | 72  |

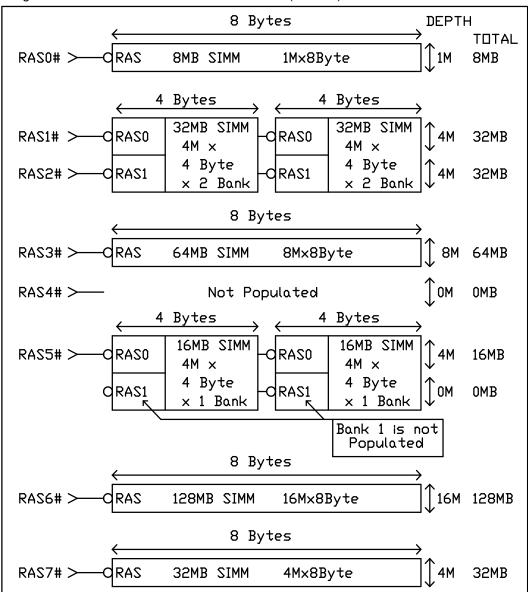

| Figure 5-4.  | Example Memory Bank Configuration                              | 79  |

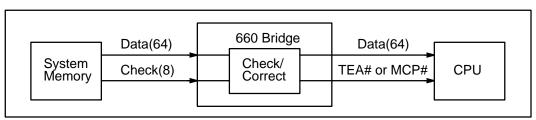

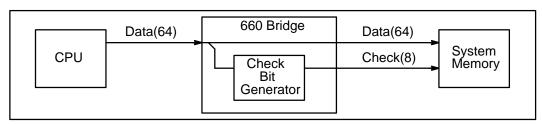

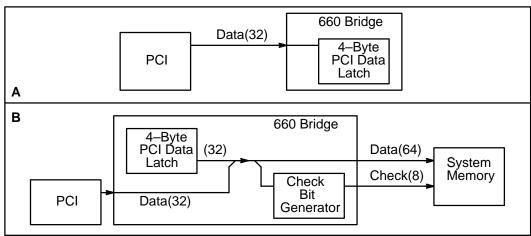

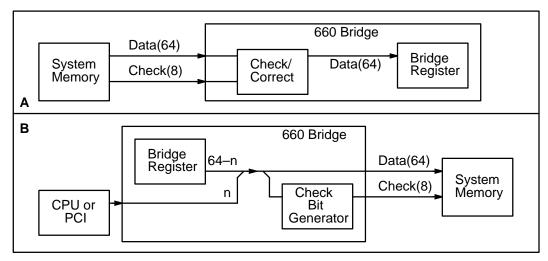

| Figure 5-5.  | CPU Read Data Flow                                             | 82  |

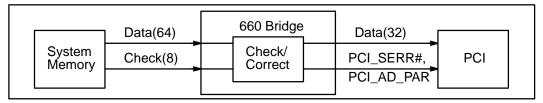

| Figure 5-6.  | PCI Read Data Flow                                             | 83  |

| Figure 5-7.  | CPU 8-Byte Write Data Flow                                     | 83  |

| Figure 5-8.  | PCI 8-Byte Write Data Flow                                     | 83  |

| Figure 5-9.  | PCI or CPU Read-Modify-Write Data Flow                         | 84  |

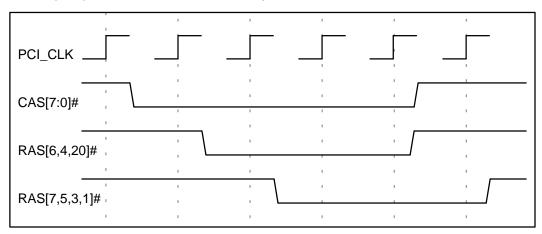

| Figure 5-10. | DRAM Refresh Timing Diagram                                    | 89  |

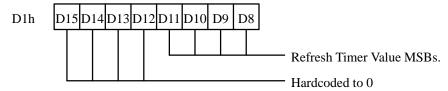

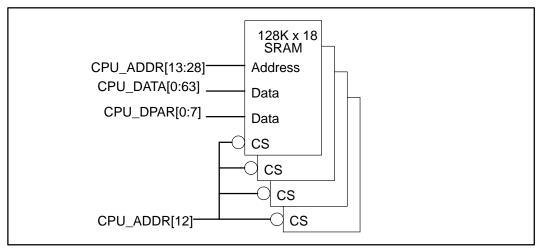

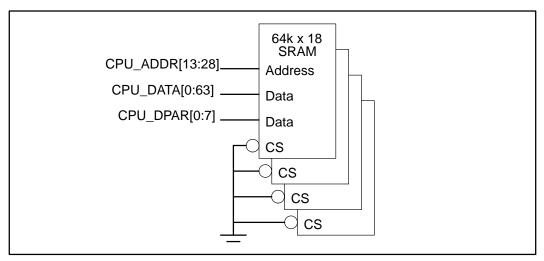

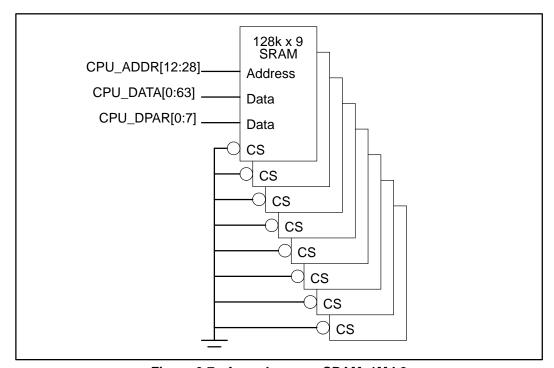

| Figure 6-1.  | Synchronous SRAM, 256K L2                                      | 98  |

| Figure 6-2.  | Synchronous SRAM, 512K L2                                      | 98  |

| Figure 6-3.  | Preferred Synchronous SRAM, 1M L2                              | 99  |

| Figure 6-4.  | Alternate Synchronous SRAM, 1M L2                              | 99  |

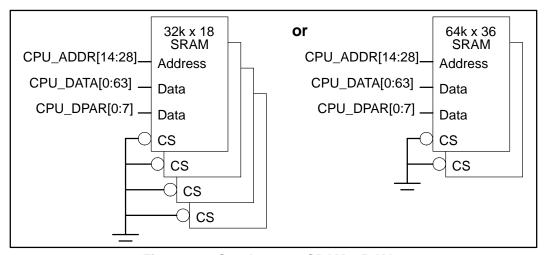

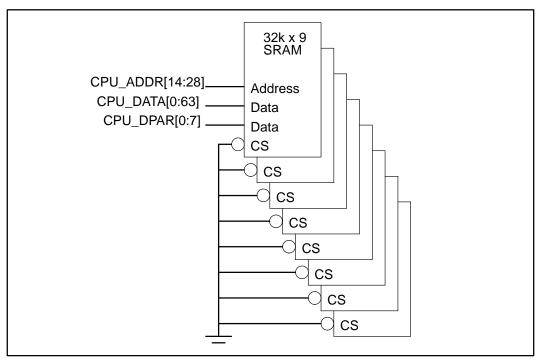

| Figure 6-5.  | Asynchronous SRAM, 256K L2                                     | 100 |

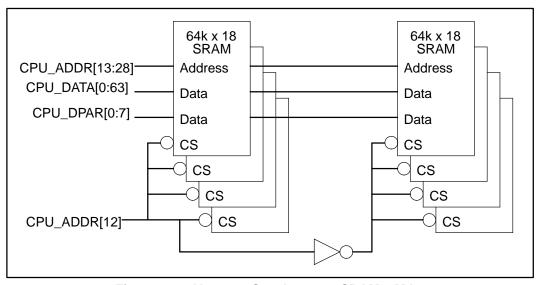

| Figure 6-6.  | Asynchronous SRAM, 512K L2                                     | 100 |

| Figure 6-7.  | Asynchronous SRAM, 1M L2                                       | 101 |

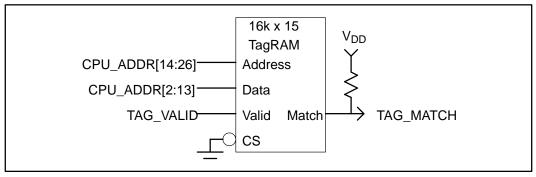

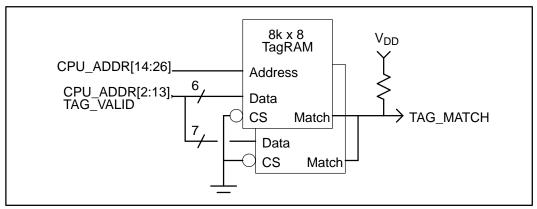

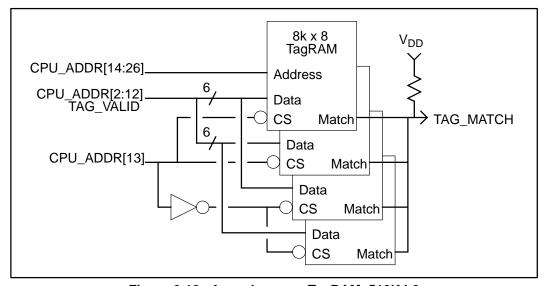

| Figure 6-8.  | Synchronous TagRAM, 256K L2                                    | 102 |

| Figure 6-9.  | Synchronous TagRAM, 512K L2                                    |     |

| Figure 6-10. | Synchronous TagRAM, 1M L2                                      | 102 |

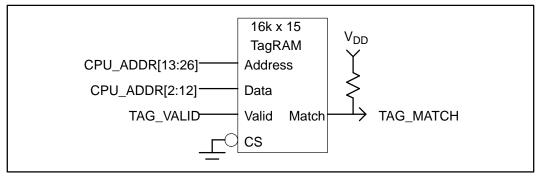

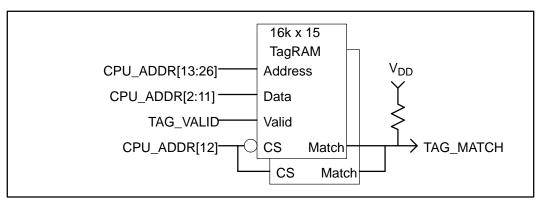

| Figure 6-11. | Asynchronous TagRAM, 256K L2                                   | 103 |

| Figure 6-12. | Asynchronous TagRAM, 512K L2                                   | 103 |

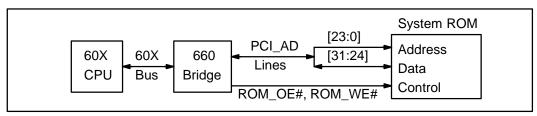

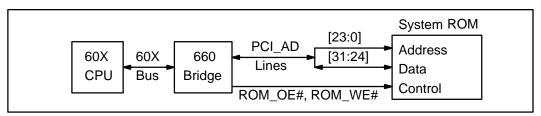

| Figure 7-1.  | ROM Connections                                                | 108 |

| Figure 7-2.  | ROM Read Timing Diagram                                        | 109 |

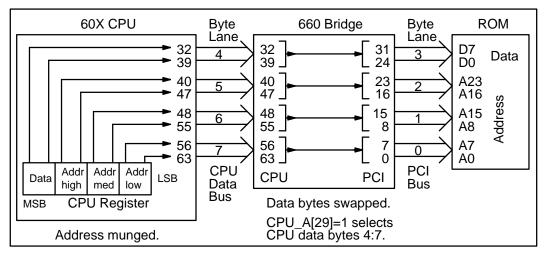

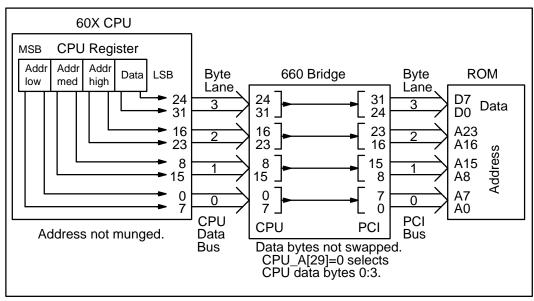

| Figure 7-3.  | ROM Connections                                                |     |

| Figure 7-4.  | ROM Data and Address Flow In Little Endian Mode                | 112 |

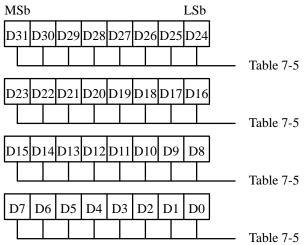

| Figure 7-5.  | ROM Data and Address Flow In Big Endian Mode                   | 113 |

|              |                                                                |     |

## PowerPC"

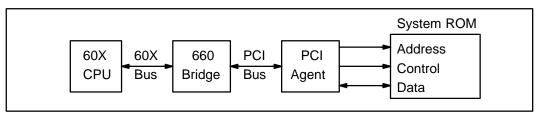

| Figure 7-6.  | Remote ROM Connections                                                                 | 114 |

|--------------|----------------------------------------------------------------------------------------|-----|

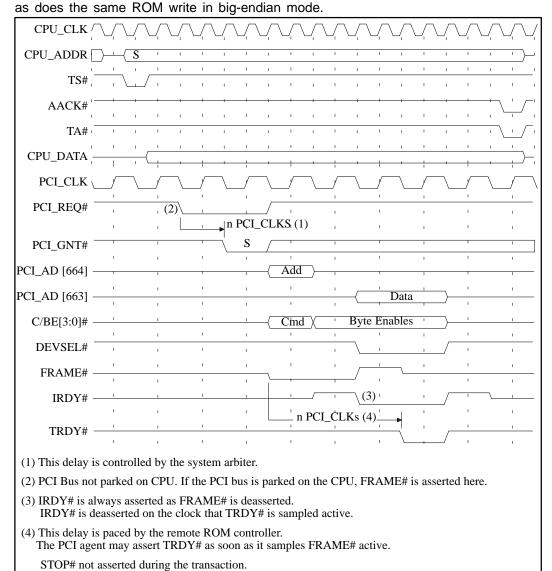

| Figure 7-7.  | Remote ROM Read – Initial Transactions                                                 | 115 |

| Figure 7-8.  | Remote ROM Read – Final Transactions                                                   | 116 |

| Figure 7-9.  | Remote ROM Write                                                                       | 119 |

| Figure 8-1.  | Conceptual Block Diagram of INT Logic                                                  | 127 |

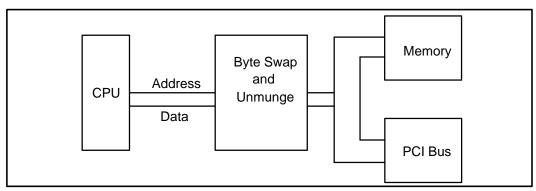

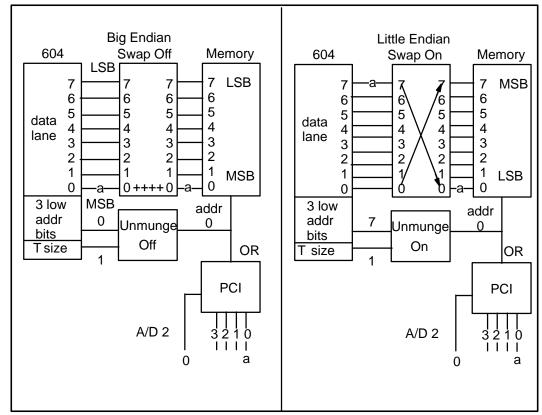

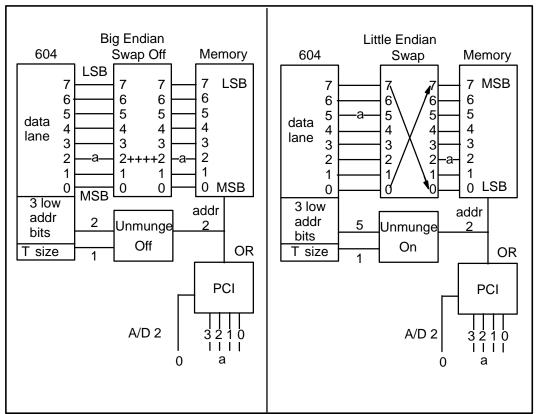

| Figure 9-1.  | Data Flow Location of 660 Byte Swapper                                                 | 147 |

| Figure 9-2.  | One Byte Transfer at Address xxxx xxx0                                                 | 150 |

| Figure 9-3.  | One Byte Transfer at Address xxxx xxx2                                                 | 151 |

| Figure 9-4.  | Two Byte Transfer at Address xxxx xxx0                                                 | 152 |

| Figure 9-5.  | Four Byte Transfer at Address xxxx xxx4                                                | 153 |

| Figure 9-6.  | Eight Byte Transfer at Address xxxx xxx0                                               | 154 |

| Figure 10-1. | BCR Configuration Information Flow                                                     | 166 |

| Figure A-1.  | Switching Levels                                                                       | 210 |

| Figure A-2.  | Signal Timing Conventions                                                              | 212 |

| Figure A-3.  | CPU_CLK to SYSCLK Skew                                                                 | 213 |

| Figure A-4.  | CPU_CLK Duty Cycle                                                                     | 213 |

| Figure A-5.  | CPU_CLK to PCI_CLK Skew                                                                | 214 |

| Figure A-6.  | CPU to Memory Write (Page DRAM) From Bus Idle                                          | 221 |

| Figure A-7.  | CPU to Memory Write (Page DRAM) Followed by Write Hit                                  | 222 |

| Figure A-8.  | CPU to Memory Write (Page DRAM) Followed by Write Page Miss and Bank Miss              | 223 |

| Figure A-9.  | CPU to Memory Write (Page DRAM) Followed by Read Hit                                   | 224 |

| Figure A-10. | CPU to Memory Write (Pg. DRAM) Read/Modify/Write From Bus Idle                         |     |

| Figure A-11. | CPU to Memory Read (Page DRAM) From Bus Idle                                           |     |

| Figure A-12. | CPU to Memory Read (Page DRAM) Followed by Read Hit                                    | 227 |

| Figure A-13. | CPU to Memory Read (Page DRAM) Followed by Read Miss and Bank Miss                     |     |

| Figure A-14. | CPU to Memory Read (Page DRAM) Followed by Write Hit                                   |     |

| Figure A-15. | CPU to Bridge Write of Bridge Control Register                                         |     |

| Figure A-16. | CPU to Bridge Read of ROM                                                              |     |

| Figure A-17. | CPU to Bridge Read of Bridge Control Register                                          |     |

| Figure A-18. | CPU to Memory Read, L2 Cache w/Async SRAMS, Hit                                        |     |

| Figure A-19. | CPU to Memory Read, L2 Cache w/Burst SRAMs, Hit                                        |     |

| Figure A-20. | CPU to Memory Read (EDO DRAM) Cache Miss Followed by Read Hit Cache Miss w/Async SRAMs |     |

| Figure A-21. | CPU to Memory Read (EDO DRAM) Cache Miss Followed by Read Hit Cache Miss w/Burst SRAMs |     |

| Figure A-22. | CPU to Memory Read (EDO DRAM) Followed by Read Hit                                     |     |

| Figure B-1.  | 653 Package/Pin Electrical Model                                                       |     |

| Figure B-2.  | 663 Buffer Package Drawing                                                             |     |

| Figure B-3.  | 664 Controller Package Drawing                                                         |     |

| -            |                                                                                        |     |

## **Tables**

| Table 2-1.  | 660 Bridge Signal Descriptions                                |    |

|-------------|---------------------------------------------------------------|----|

| Table 3-1.  | TT[0:3] (Transfer Type) Decoding by 660 Bridge                |    |

| Table 3-2.  | 660 Bridge Address Mapping of CPU Bus Transactions            | 23 |

| Table 3-3.  | PCI Configuration Addresses                                   | 26 |

| Table 3-4.  | Types of Snoop Cycles for PCI to Memory Operations            | 34 |

| Table 4-1.  | 660 Bridge Responses to PCI_C/BE[3:0] Bus Commands            | 40 |

| Table 4-2.  | 660 Bridge Mapping of PCI Memory Space                        | 41 |

| Table 4-3.  | PCI to Memory Read Burst Sequence Timing                      | 44 |

| Table 4-4.  | PCI to Memory Write Burst Sequence Timing                     | 45 |

| Table 5-1.  | Memory Timing Parameters                                      | 53 |

| Table 5-2.  | General Case Aggressive DRAM Timing Summary                   | 63 |

| Table 5-3.  | General Case Conservative DRAM Timing Summary                 | 64 |

| Table 5-4.  | Special Case DRAM Timing Summary                              | 66 |

| Table 5-5.  | Supported SIMM Topologies                                     | 73 |

| Table 5-6.  | Row Addressing (CPU Addressing)                               | 74 |

| Table 5-7.  | Column Addressing (CPU Addressing)                            | 74 |

| Table 5-8.  | Row Addressing (PCI Addressing)                               | 74 |

| Table 5-9.  | Column Addressing (PCI Addressing)                            | 74 |

| Table 5-10. | Example Memory Bank Addressing Mode Configuration             | 78 |

| Table 5-11. | Example Memory Bank Starting and Ending Address Configuration | 80 |

| Table 5-12. | Bridge Response to Various PCI Write Data Phases              |    |

| Table 5-13. | Bridge Response to Best Case PCI Write Burst                  | 86 |

| Table 5-14. | Bridge Response to Case 2 PCI Write Burst                     | 86 |

| Table 5-15. | Bridge Response to Various PCI Write Bursts                   | 86 |

| Table 5-16. | Check Bit Calculation                                         | 87 |

| Table 5-17. | Syndrome Decode                                               | 88 |

| Table 5-18. | Typical DRAM Module Maximum Input Capacitance                 | 92 |

| Table 6-1.  | L2 Cache Responses to CPU Bus Cycles                          | 94 |

| Table 6-2.  | L2 Operations for PCI to Memory Transactions, Non-603 Mode    | 95 |

| Table 6-3.  | L2 Operations for PCI to Memory Transactions, 603 Mode        | 95 |

| Table 6-4.  | Index of SRAM and TagRAM Example Configurations               | 97 |

| Table 7-1.  | ROM Read Data and Address Flow 1                              | 10 |

| Table 7-2.  | ROM Write Data Flow in Little-Endian Mode                     | 12 |

| Table 7-3.  | ROM Write Data Flow in Big-Endian Mode 1                      |    |

| Table 7-4.  | Remote ROM Read Sequence, CPU Address = FFFX XXX0 1           | 17 |

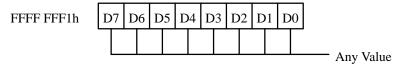

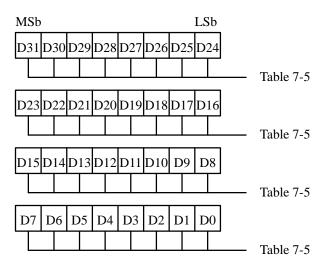

| Table 7-5.  | ROM Write BCR Contents                                        | 20 |

| Table 8-1.  | 664 Pin Reset State                                           | 24 |

| Table 8-2.  | 663 Pin Reset State                                           | 25 |

|             |                                                               |    |

| Table 8-3.  | Configuration Strapping Options                               | . 125 |

|-------------|---------------------------------------------------------------|-------|

| Table 8-4.  | Invalid CPU Bus Operations                                    |       |

| Table 8-5.  | LSSD Test Mode Pin Definitions                                |       |

| Table 9-1.  | Endian Mode Operations                                        | . 145 |

| Table 9-2.  | CPU LE Mode Address Transform                                 |       |

| Table 9-3.  | 660 Endian Mode Byte Lane Steering                            | . 147 |

| Table 9-4.  | 660 Bit Transfer                                              | . 149 |

| Table 10-1. | Direct-Access BCRs With Section References                    | . 165 |

| Table 10-2. | Indexed BCR Listing                                           | . 180 |

| Table A-1.  | 663 Buffer Timing By Signal                                   | . 215 |

| Table A-2.  | 664 Controller Timing By Signal                               | . 217 |

| Table B-1.  | Absolute Maximum Ratings, 660 Bridge                          | . 239 |

| Table B-2.  | Recommended Operating Conditions, 660 Bridge                  | . 240 |

| Table B-3.  | 660 Power Dissipation                                         | . 240 |

| Table B-4.  | Typical Thermal Resistance, Junction to Ambient, No Heat Sink | . 241 |

| Table B-5.  | Common Characteristics                                        | . 241 |

| Table B-6.  | Electrical Model Range of Values                              | . 242 |

| Table B-7.  | 663 DC Characteristics By Signal                              | . 243 |

| Table B-8.  | 664 DC Characteristics By Signal                              | . 244 |

### **About This Book**

#### Audience:

This book is designed for engineers who are familiar with the PowerPC family of processors and the PCI bus.

#### **Reference Material:**

- PowerPC 604 User's Manual, IBM document MPR604UMU-01.

- PowerPC 603 User's Manual, IBM document MPR603UMU-01.

- PowerPC 603e User's Manual, IBM document MPR603EUMU-01.

- PowerPC 601 User's Manual, IBM document MPR601UMU-02.

- PCI Local Bus Specification, Revision 2.1, available from the PCI SIG.

- 32MB SIMM Engineering Specification, IBM document number MMDL02DSU-00.

- 8MB SIMM Engineering Specification, IBM document number MMDL01DSU-00.

- PowerPC Reference Platform Specification, Version 1.1, IBM document MPRPRPKG-02.

- The Power PC Architecture, second edition, Morgan Kaufmann Publishers (800) 745–7323, IBM document MPRPPCARC-02.

- PowerPC System Architecture, Tom Shanley, Mindshare, Inc., Addison-Wesley Publishing 1–800–822–6339 (Order # 0–201–40990–9).

- IBM PowerPC 603/604 Reference Design Technical Specification, IBM document MPRH01TSU-02.

- PowerPC 604 SMP Reference Design Technical Specification, IBM document MPRZAPTSU-04.

- Open Programmable Interrupt Controller (PIC) Register Interface Specification, Revision 1.2.

- FAQ and application notes are available at http://www.chips.ibm.com/products/ppc/apnote\_files/index.html

The example implementation schematics have been replaced by the *IBM PowerPC 603/604 Reference Design Technical Specification* and the *PowerPC 604 SMP Reference Design Technical Specification*.

#### **Document Conventions:**

xxii

Kilobytes, megabytes, and gigabytes are indicated by a single capital letter after the numeric value. For example, 4K means 4 kilobytes, 8M means 8 megabytes, and 4G means 4 gigabytes.

In this document a word is 32 bits, a double-word is 64 bits, and a half-word is 16 bits.

The term SIMM is often used to mean DRAM module.

Hexadecimal values are identified (where not clear from context) with a lower-case letter h at the end of the value. For example, 001Fh means a hex value of 1F. Binary values are identified (where not clear from context) with a lower-case letter b at the end of the value. For example, 0101b means a 4-bit binary value of 0101.

The range statement from 0 to 2M means from and including zero up to (but not including) two megabytes. The hexadecimal value for the range from 0 to 64K is: 0000h to FFFFh.

The terms *asserted* and *negated* are used extensively. The term *asserted* indicates that a signal is active (logically true), regardless of whether that level is represented by a high or low voltage. The term *negated* means that a signal is not asserted. The # symbol at the end of a signal name indicates that the active state of the signal occurs with a low voltage level.

Signal ranges are always shown with the most significant number first (SIGNAL[MSb:LSb]). Signals ranges that have the first number greater than the second number (PCI\_AD[31:0]) are shown in little-endian nomenclature. Those shown with the second number greater than the first (TT[0:3] for example), are shown using big-endian nomenclature. Signal range names used without an explicit range indication refer to the entire set of signals (PCI\_AD means PCI\_AD[31:0]).

#### **Acronyms and Abbreviations:**

The term 60X CPU and CPU refers to the PowerPC 601, 603, and 604 families of microprocessors, generally including "e" versions.

The term I/O Bridge or I/O Bus Bridge refers to a PCI master that serves to connect the PCI bus to a PC-standard bus like the ISA, EISA, or MicroChannel buses.

The term write-back means the same as copy-back in reference to a mode of cache operation.

The IBM 27-82660 is generally referred to as the Bridge, the 660 Bridge, or the 660; likewise, the IBM27-82664 is generally called the 664 Controller or the 664. Also, the IBM27-82663 is generally called the 663 Buffer or the 663.

#### **Contributors:**

This document was written and edited by Ben Drerup and Dale Elson, with substantial contributions by Robert Stevens, Sean Curry, and the Kauai-Lanai design, simulation, and testing team.

Figure 1-1. IBM 660 Bridge Chip Set in a Typical System Configuration

#### Section 1 Overview

This section summarizes the features of the 660 Bridge—including microprocessor support, the memory controller, the PowerPC CPU bus, the PCI expansion bus, the L2 cache controller, the system ROM controller, the bridge control register set, and the interrupt and exception handler.

- Complies with the PowerPC Reference Platform specification, versions 1.0 & 1.1

- Complies with the PCI Revision 2.0 & 2.1 specification.

#### 1.1 Packaging and Technology

- Designed in IBM YASU 3.3 to 3.6V CMOS4LP logic which allows I/Os that are compatible with 3.3V and 5.0V logic

- 208-pin (664) and 240-pin (663) low-cost plastic wire-bond flatpacks

- Operates from 3.0V to 3.78V, allowing either 3.3V or 3.6V power sources.

#### 1.2 Microprocessor Support

- Supports PowerPC 601, 603, 603e(v), 604, and 604e(v) microprocessor families

- Supports CPU bus speeds up to 66Mhz. Internally, the CPU can run at a faster rate

- Directly supports two CPU bus masters

- · Supports little-endian and big-endian operating modes

- 64 bit wide CPU data bus and 32 bit wide CPU address bus

- · Utilizes address bus pipelining

- Dual bus structure between CPU bus and PCI bus

- Data path latches enhance effective bandwidth

- Supports all clock modes for CPUs (internal CPU clock to CPU bus)

- The MCP# signal on the 603 and 604 is supported for error reporting

- For reduced read latency, the no-DRTRY# mode of the 604 is supported

- The 603 no-DRTRY# mode is also supported except when the 603 is in 1:1 mode

- The 601 is always in DRTRY# mode

- Error reporting is by means of TEA# or MCP# on the 603 and 604

- Error reporting is by means of TEA# and INT\_CPU# on the 601

- The 604 store multiple 8-byte transfer is supported to the PCI bus

#### 1.3 L2 Cache Controller

- · Controls external burst-mode or asynchronous SRAMs for cached data

- · Controls external tag RAMs for tag information

- · Look-aside, direct-mapped, and write-through protocols

- · Supports all cache sizes

- Externally determined cache size

- Responds to snoop cycles for PCI reads and writes of system memory

- Option to check parity of data stored in L2 on read cycles

- L2 cache controller can be disabled if external L2 cache is used.

#### 1.4 PCI Expansion Bus

- PCI bus frequency up to 33 MHz. CPU:PCI bus ratios of 1:1 and 2:1 supported.

- 32-bit multiplexed PCI address and data path

- Support for I/O bus bridge (ISA, EISA, MicroChannel<sup>™</sup>)

- PCI to DRAM access—with L1 and L2 cache snooping

- Support for memory mapping of 60X address space into PCI transactions

- · Supports ISA bus master access to system memory with ISA bridge on the PCI bus

- Supports contiguous ISA I/O and non-contiguous ISA I/O mappings (non-contiguous I/O so operating systems can memory-protect 32-byte blocks of ISA I/O space)

- Uses external PCI arbiter (usually from the I/O bridge chip)

- Support for PCI resource locking of system memory

- Supports type 0 and type 1 PCI configuration cycles.

#### 1.5 Memory Controller

- Supports memory operations for the PowerPC Architecture™

- Data bus path 72 bits wide—64 data bits and eight bits of optional ECC or parity data

- Supports Eight SIMM sockets, with empty SIMM sockets allowed at any position

- Eight RAS# outputs, eight CAS# outputs, and two write-enable outputs

- Supports industry-standard 8-byte (168-pin) SIMMs of 8M, 16M, 32M, 64M, and 128M that can be individually installed for a minimum of 8M and a maximum of 1G

- Supports industry-standard 4-byte (72-pin) SIMMs of 4M, 8M, 16M, 32M, 64M, and 128M that must be installed in pairs for a minimum of 8M and a maximum of 1G

- Programmable memory timings enable optimization of DRAM timings for a large variety of CPU bus frequencies, DRAM speeds, and system topologies

- Mixed use of different size SIMMs, including mixed 4-byte and 8-byte SIMMs

- Support for parity, ECC, or neither

- Generates ECC or even parity, eight bits for eight bytes, on all memory writes

- · Checks ECC or parity eight-bytes wide on all memory reads

- · Detects and corrects all single-bit errors in ECC mode

- Detects all two-bit errors in ECC mode

- Page-mode access—fast page-mode is supported

- Support for extended-data-out (EDO) DRAM (hyper-page mode) for higher bandwidth memory performance

- Provides row-address and column-address multiplexing for SIMMs requiring:

- 10 row by 10 column

- 11 row by 10 column

- 12 row by 10 column and 11 row by 11 column (supported simultaneously)

- 12 row by 11 column

- 12 row by 12 column

- Non-interleaved memory access operation

- Programmable DRAM refresh timer with low-power mode

- · Memory refresh address counter

- Burst-mode memory address generation logic

- 32-byte CPU bursts to and from memory

- Variable length PCI burst to and from memory

- Little-endian and big-endian modes

- Supports ISA master to DRAM access

#### Minimum Cycle Times For Pipelined CPU to Memory Transfers at 66 MHz

|                             | -        |          |

|-----------------------------|----------|----------|

| Responding Device           | Read     | Write    |

| L2 (9ns Synchronous SRAM)   | -2-1-1   | Snarf    |

| L2 (15ns Asynchronous SRAM) | -3-2-2-2 | Snarf    |

| Page DRAM (70ns) Pipelined  | -4-4-4   | -3-3-4-4 |

| EDO DRAM (60ns) Pipelined   | -5-3-3-3 | -3-3-3-3 |

Other minimum timings at 66MHz CPU and 33MHz PCI and 70ns page mode DRAM:

- PCI to memory read:

- 8-1-1-1 -1-1-1 7-1-1-1 1-1-1-1 7-1-1-1 ... 7-1-1-1 ... 7-1-1-1 (PCI clocks)

- PCI to memory write:

- 5-1-1-1 -3-1-1-1 3-1-1-1 3-1-1-1 3-1-1-1 ... 3-1-1-1 -3-1-1-1 (PCI clocks)

#### 1.6 System ROM Controller

- Supports ROM attached to PCI\_AD bus

- Supports 8-bit flash ROM

- Provides 8-bit to 64-bit conversion on reads

- 21-bit address support for up to 2M addressable ROM

- Flash ROM write cycles generated for in-system flash ROM writes

- Flash ROM write lock-out support

- · Single-beat (one-byte to eight-byte) read cycle

- Single-beat (one-byte) write cycle

- Pseudo burst-mode (32-byte) read cycle.

#### 1.7 The Bridge Control Register Set

- Implemented PCI register model

- Includes 650 Bridge-compatible registers

- · Configuration through register 0CF8h and 0CFCh configuration method

- · Chip set options are configured in the register set

- Allows extensive and flexible programming of the 660.

#### 1.8 Interrupt and Exception Handler

- 603/604 error reporting by means of TEA# or MCP#

- 601 error reporting by means of TEA#, or INT\_CPU# and TEA#

- · Supports error address and control capture registers

- Reports the following types of errors:

- Memory parity or ECC error

- CPU illegal transfer

- PCI bus parity error

- · CPU data bus parity error

- PCI cycle abort

- L2 cache parity error

- Write to locked flash ROM

- Memory access out of range

- Drives CPU data lines to all one-bits on out-of-range memory reads

- PCI configuration read cycles return all one-bits when no device responds.

#### 1.9 Part Identification, IBM27-82660

The release version of the 660 is revision 2.2.

| IBM27-82660      | IBM27-826 | 663 (663 Buffer)     | IBM27-82664 (664 Controller) |                      |  |

|------------------|-----------|----------------------|------------------------------|----------------------|--|

| Chipset Revision | Revision  | Package Mark-<br>ing | Revision                     | Package Mark-<br>ing |  |

| 1.0              | 1.0       | 94G0235              | 1.0                          | 94G0232              |  |

| 1.1              | 1.0       | 94G0235              | 1.1                          | 94G0176              |  |

| 2.0              | 2.0       | 94G0178              | 1.1                          | 94G0176              |  |

| 2.2              | 2.0       | 94G0178              | 1.2                          | 20H2842              |  |

#### 1.10 Improvements Over 650 Bridge

- Includes L2 cache controller that supports synchronous and asynchronous SRAMs

- System performance improvements:

- Programmable memory controller optimizes to memory speed and topology

- Support for high-bandwidth memory technology (extended-data-out DRAM)

- Up to 1G addressable DRAM

- Utilizes CPU bus address pipelining

- Dual bus structure between CPU bus and PCI bus

- Data path latches provide bandwidth improvements

- ECC memory support

- Supports 603 in 1-to-1 mode (60X internal clock vs. CPU bus)

- The 604 store multiple 8-byte transfer is supported to the PCI bus

- Low-cost packaging—a 208-pin and a 240-pin plastic quad flatpack

- · Uses an external PCI bus arbiter

- · Provides basic multi-processor support

- Supports type 1 PCI configuration cycles in addition to type 0

- · Implements Expanded error control and reporting

- Provides a DRAM refresh timer

- Implements PCI-compatible configuration register set.

#### 1.11 Chipset Changes From Prerelease Versions

This section describes changes that were made to the 660 bridge during development, especially as reflected in the differences between this document (SC09-3026-00) and A previous revision (MPR660UMU-01) of the 660 User's Manual. Many of these items were noted in *The IBM27-82660 Revision 2.1 Product Update* (MPR660ESU-04). At the time of the printing of this document, there were no known errata associated with the 660.

#### 1.11.1 CPU RDL OPEN Resistor

Add a  $200\Omega$  series resister to the CPU\_RDL\_OPEN net between the 664 and the 663. See section 2.2.

#### 1.11.2 Parity Error Detection

Parity errors on the CPU and memory data busses are only detected by the 663 if there are an odd number of bit errors. All single bit errors are detected. See section 5.4.1.

#### 1.11.3 ECIWX/ECOWX With 603

ECIWX and ECOWX are not supported for use in systems containing a 603 or 603e that is running at a 1:1 or 3:2 CPU core:bus clock ratio. These instructions are supported for systems featuring a 601, 604 or 604e CPU.

#### 1.11.4 Error Simulation Registers

Error simulation BCRs 1 and 2 are not supported, and have been removed from the BCR section.

#### 1.11.5 DRAM Performance

The DRAM performance and memory controller programming guidelines in the DRAM section have changed, as shown especially in section 5.2, DRAM Performance.

A special case has been identified which is described in section 5.2.4. Designers may wish to avoid this case or to incorporate a performance enhancement strategy.

#### 1.11.6 CAS# Pulse Width

Setting the CAS# pulse width to four CPU clocks is not supported. See the Memory Timing Register 2 description (section 10.3.29).

#### 1.11.7 CPU:PCI Bus Ratio

Operation of 660 systems at a CPU:PCI bus ratio of 2:1 is supported. Operation at 3:1 is not supported, and has been removed from the Introduction (section 1.4) and PCI Bus (section 4) sections.

Operation at 1:1 is supported only with the use of external logic, and only while the PCI arbiter is programmed to not park the PCI bus on the 660 (see section 4.6).

#### 1.11.8 Parking the PCI Bus on the 660

If the CPU:PCI clock ratio is 2:1, and the PCI arbiter is programmed to park the PCI bus on the 660 (see section 4.1), and the 660 is in one of the following configurations:

- 1. Configuration 1:

- 1.1 Possible 70ns timings (see section 5.2.1), of:

- 1.1.1 RAS# precharge (RP) = 4 (CPU clocks), and

- 1.1.2 RAS# to CAS# delay (RCD) = 3, and

- 1.1.3 CAS# pulse width (CPW) = 3. And

- 1.2 L2 type set to Asynchronous (see section ), or

- 2. Configuration 2:

- 2.1 Possible 70ns timings (see section 5.2.1), of:

- 2.1.1 RAS# precharge (RP) = 4, and

- 2.1.2 RAS# to CAS# delay (RCD) = 3, and

- 2.1.3 CAS# pulse width (CPW) = 3. And

- 2.2 ECC memory checking enabled (see section), or

- 3. Configuration 3:

- 3.1 Possible 60ns timings (see section 5.2.1), of:

- 3.1.1 RAS# precharge (RP) = 3, and

- 3.1.2 RAS# to CAS# delay (RCD) = 3, and

- 3.1.3 CAS# pulse width (CPW) = 3. And

- 3.2 L2 type set to Asynchronous (see section), and

- 3.3 ECC memory checking enabled (see section),

then program the PCI arbiter to not park the PCI bus on the 660. This typically results in adding two PCI clocks to the latency of CPU to PCI transactions, and typically reduces the latency of PCI to memory accesses by one PCI clock.

#### 1.11.9 CPU Data Bus Parity With 64-Bit L2

When using 64-bit L2 SRAM, CPU bus parity error detection and L2 cache parity error detection must be disabled. No changes to operation with 72-bit SRAM or no SRAM. See section 6.4, L2 Error Checking Support.

#### 1.11.10 ECC Single-Bit Error Counter BCR(B8h)

The bit ordering of this BCR is reversed. See section 10.3.33, Single-Bit Error Counter Register.

#### 1.11.11 663 Pinout

The pinout of the 663 was rearranged to reduce ground bounce effects by distributing simultaneously switched signals more evenly around the perimeter of the device.

#### 1.11.12 Added Signals

DBG# was added to the 664 Controller to support a 604 in fast L2 mode. This change is documented in the MPR660UMU-01 release of the 660 Bridge User's Manual, and is noted here for completeness.

PCI\_TRDY# was connected to the 663 to improve performance.

#### 1.11.13 Remote ROM

Remote ROM is supported as detailed in section 7. Information about remote ROM operation was removed from the -02 version of this document. All references to remote ROM operation have been restored to the documentation.

#### 1.11.14 Power Management

Power management is not supported. Power management has been removed from the Additional Information section. The description of the Bridge Chipset Options 2 BCR (section10.3.36) has been changed. The Suspend Refresh Timer Register BCR(D3:D2) has been removed.

#### 1.11.15 VI Curves

VI curves for the output drivers are not supplied by IBM. SPICE model information is available from IBM under Non-Disclosure Agreement. Contact your IBM technical representative for more information.

#### 1.11.16 CPU Data Bus Resistors

To improve output signal quality,  $33\Omega$  series resistors were added to the 663 buffer connections to the CPU data bus lines CPU\_DATA[0:63] and CPU\_DPAR[0:8]. Each resister is placed between the 663 pin and all other CPU bus agent(s) attached to the net. For maximum benefit, place the series resistors as close to the 663 package as is feasible.

Figure 2-1. 660 Bridge Pin Connections

2

### Section 2 Pin Descriptions

This section describes the connectivity of the 660 Bridge. See Figure 2-1.

The terms asserted and active indicate that a signal is logically true, regardless of the voltage level. The terms negated, inactive, and deasserted mean that a signal is logically false.

The # symbol at the end of a signal name listed in Table 2-1 indicates that the active or asserted state of the signal occurs with a low voltage level. Otherwise the signal is active at a high voltage level.

Pins which are marked s/t/s are sustained tri-state. This is an active low tri-state signal owned and driven by one agent at a time. The agent that drives the s/t/s pin active low must actively drive it high before letting it float. On the PowerPC bus, this is known as the restore function. On the PCI bus, the agent must drive the signal high for one clock and then tristate it. A new agent cannot drive the pin any sooner than one clock after the previous owner tri-states it. An external pull-up is required to maintain the inactive state.

Appendix C contains numeric and alphabetic lists of the pins in the 663 Buffer and 664 Controller. These lists include pin numbers.

### 2.1 Signal Description Table

Table 2-1. 660 Bridge Signal Descriptions

| Signal Name       | 663 | 664        | Description                                                                                                                        |  |

|-------------------|-----|------------|------------------------------------------------------------------------------------------------------------------------------------|--|

| CPU Bus Interface |     |            |                                                                                                                                    |  |

| AACK#             | _   | I/O<br>109 | CPU address acknowledge. 660 asserts AACK# to signal the end of the current address tenure.                                        |  |

|                   |     |            | AACK# is an input to the 664 when a CPU bus target claims the current transaction by means of CPU_BUS_CLAIM#.                      |  |

| ARTRY#            | _   | I/O<br>110 | Address retry. ARTRY# is asserted by a CPU bus device to signal that the current address tenure needs to be rerun at a later time. |  |

|                   |     |            | The 660 samples ARTRY# on the second clock after TS# is sampled active.                                                            |  |

|                   |     |            | The 660 will only assert ARTRY# on the clock after it asserts AACK# (during a PCI retry).                                          |  |

Table 2-1. 660 Bridge Signal Descriptions (Continued)

| Signal Name     | 663               | 664               | Description                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |  |  |  |  |

|-----------------|-------------------|-------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|--|

| CPU Bus Interfa | CPU Bus Interface |                   |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |  |  |  |  |

| CPU_ADDR[0:31]  | _                 | I/O<br>see<br>App | CPU address bus. Represents the physical address of the current transaction. Is valid from the bus cycle in which TS# is asserted through the bus clock in which AACK# is asserted.                                                                                                                                                                                                                                                                                               |  |  |  |  |

|                 |                   | C                 | CPU_ADDR is an input to the 664 on transactions initiated by a CPU bus master. The the CPU bus target responds with AACK# when the address is no longer required, ending the address tenure.                                                                                                                                                                                                                                                                                      |  |  |  |  |

|                 |                   |                   | CPU_ADDR is an output from the 664 on system memory transactions initiated by a PCI bus master device. The 664 initiates an address tenure to snoop the address requested by the PCI bus master.                                                                                                                                                                                                                                                                                  |  |  |  |  |

| CPU_BUS_CLAIM#  | _                 | I<br>132          | CPU bus claim. This signal is asserted by a CPU bus target to claim a CPU bus memory transaction. It inhibits the 664 from driving AACK, TA#, TEA#, and the CPU data bus lines.                                                                                                                                                                                                                                                                                                   |  |  |  |  |

|                 |                   |                   | This signal is sampled by the 664 on the second CPU_CLK after TS# is sampled active. CPU bus targets can only map to system memory space (0 to 2G) and only to memory space that is not cached by the L2. The L2 caches as much of the space from 0 to 2G as is populated by DRAM. So, if 8M is installed starting at 0, the CPU_BUS_CLAIM# can be asserted from 8M to 2G. If the internal L2 is disabled, then the entire 0 to 2G memory space can be claimed by CPU_BUS_CLAIM#. |  |  |  |  |